Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

D-триггеры, управляемые по одному фронту

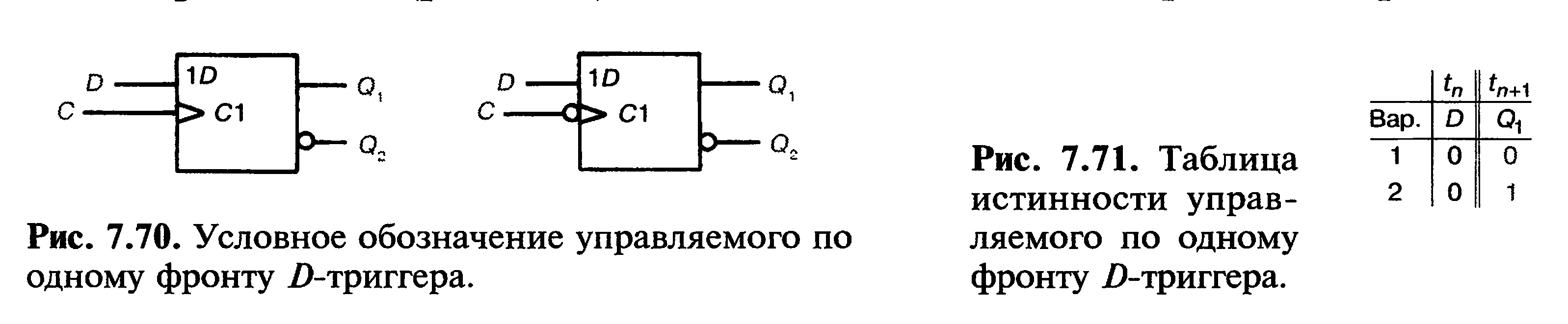

Управляемый по фронту D-триггер по структуре очень похож на тактируемый по уровню D-триггер. Эти разновидности триггера отличаются только управлением. Управляемые по одному фронту D-триггеры делятся на триггеры, управляемые прямым фронтом и обратным фронтом импульса сигнала синхронизации (рис. 7.70). Таблица истинности изображена на рис. 7.71.

После подачи управляющего фронта синхроимпульса сигнал на D-входе переходит на выход триггера и действует на выходе Q, в прямой и на выходе Q2 в инверсной форме.

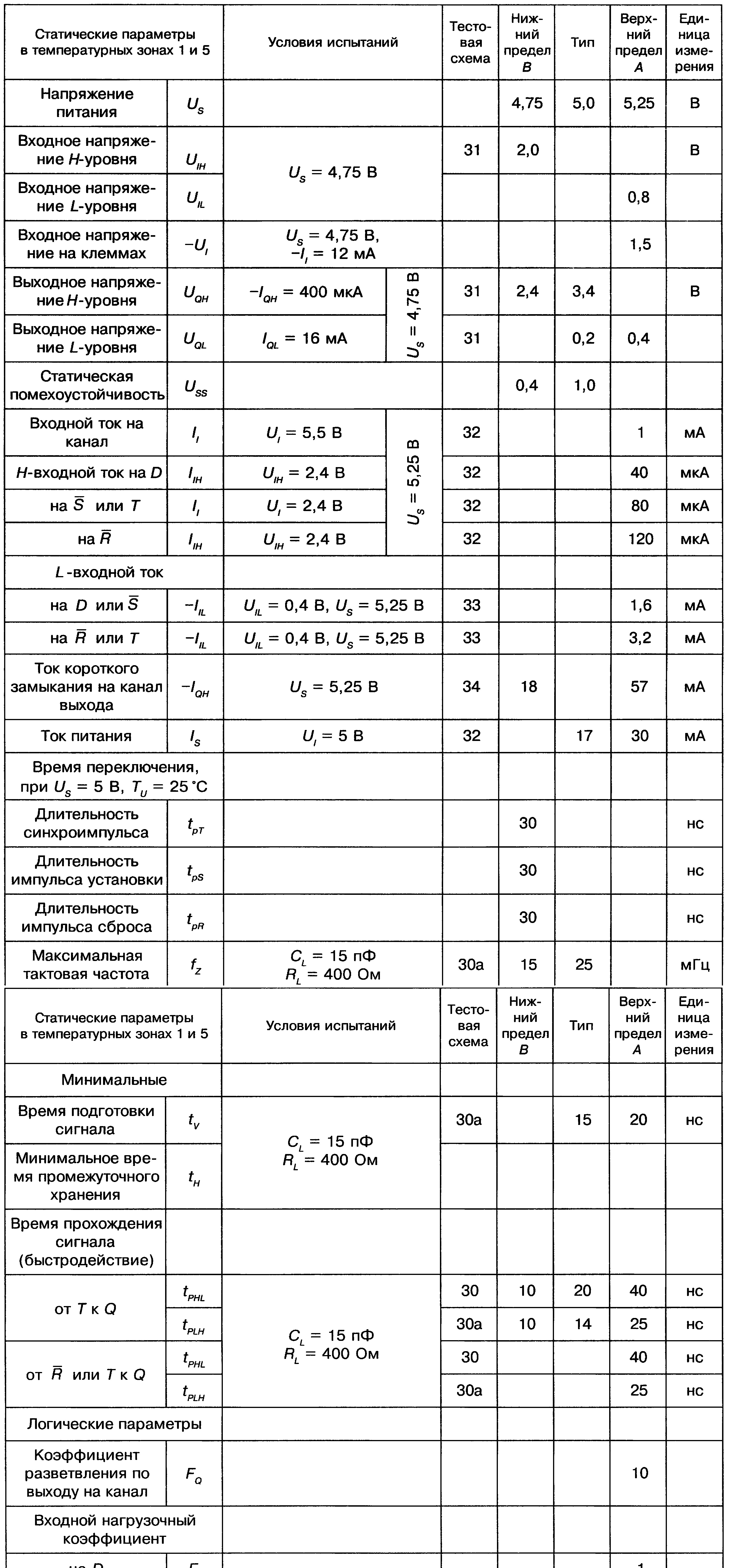

Управляемые по одному фронту D-триггеры используются прежде всего для сдвиговых регистров (см. разд. 12). На рис. 7.72 представлена таблица данных микросхемы FLJ 141-7474. Эта микросхема содержит два управляемых прямым фронтом D-триггера.

Сдвоенный D-триггер

Триггеры FLJ 141 и FLJ 145 имеют нетактируемые входы установки и сброса. Передача информации со входа D на выход Q происходит во время прямого фронта синхроимпульса, сразу после открытия входного транзистора. После этого D-вход снова запирается.

Рис. 7.72. Таблица данных микросхемы FLJ 141-7474 (по данным фирмы Siemens)

Цоколевка и принципиальная схема одного из двух D-триггеров показана на рис. 7.73.

Похожие статьи