Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Ж-триггеры, управляемые по обоим фронтам

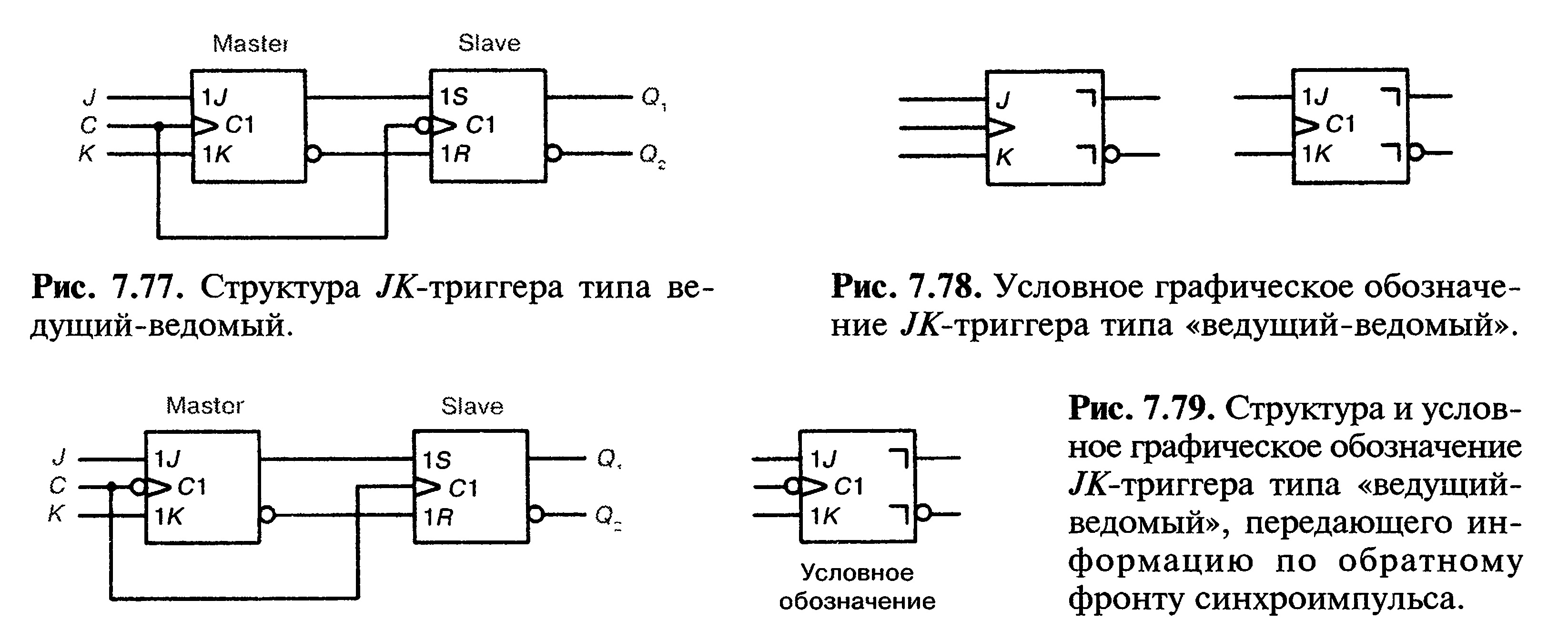

Управляемые по двум фронтам /if-триггеры, как и управляемые по двум фронтам Л^-триггеры, являются триггерами типа «ведущий-ведомый». Ведущий триггер должен быть /АТ-триггером, так как он должен переключаться при комбинации /= 1 и А^ = 1.В качестве ведомого триггера достаточно взять АУ-триггер (рис. 7.77), поскольку оба выхода /A-триггера одновременно не могут быть равны 1. Условное обозначение этого /AT-MASTEi?-SLAVE-триггера изображено на рис. 7.78. Оно отличается от условного обозначения управляемого по одному фронту /A-триггера только уголками перед выходами. Таблица истинности является такой же, как для управляемого по одному фронту /Аугриггера (см. рис. 7.65). Существуют также управляемые по двум фронтам триггеры, которые управляют ведущим триггером по обратному фронту синхроимпульса. Тогда ведомый триггер переключается по прямому фронту синхроимпульса (рис. 7.79).

В условном обозначении управляемого по двум фронтам триггера (типа «ведущий-ведомый») всегда указывается фронт синхроимпульса, по которому принимается информация. Передача информации на выход происходит по другому фронту синхроимпульса (DIN 40900, часть 12).

На рис. 7.80 представлена таблица данных микросхемы FLJ 131-7476. Эта микросхема содержит два /А-MASTER-SLAVE-триггера с не тактируемыми входами установки и сброса. Она принадлежит к TTJI-семейству. Цоколевка и принципиальная схема триггера показана на рис. 7.81.

Микросхема FU 341-74110 содержит /A'-MASTER-SLAVE-триггер с блокированием входа (рис. 7.82). Функция блокирования входа для управляемых по двум фронтам ЛУ-триггеров была рассмотрена выше. Она обеспечивает запирание входов через определенное время после завершения прямого фронта синхроимпульса. Это так называемое время промежуточного хранения составляет для схемы FLJ 341-74110 только 5 не. Сигналы помехи могут привести к ложному срабатыванию только в течение этого короткого времени. Поэтому триггер очень помехоустойчив.

Три связанные логическим умножением /-входа и три также связанные логическим умножением /Г-входа позволяют экономически выгодно производить синхронные счетчики (см. гл. 11).

Похожие статьи