Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Законы алгебры логики

Основные законы алгебры логики являются правилами, также называемыми еще аксиомами, действующими для логических операций над постоянными величинами.

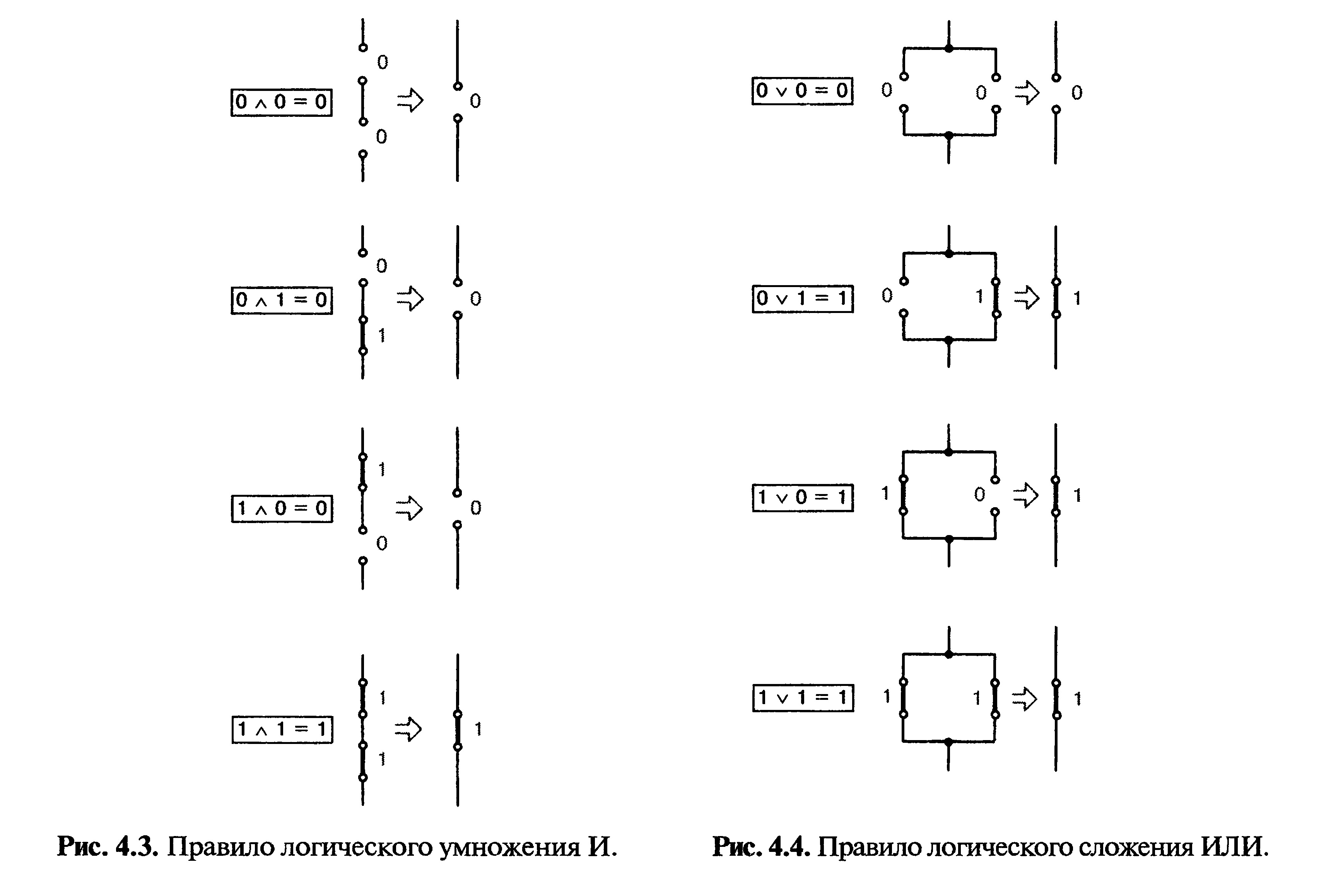

Закон для операции логического умножения И показан на рис. 4.3.

Схематично логическое умножение И можно изобразить в виде

последовательного соединения ключей. Логическая единица на выходе будет

только в том о = ! случае, если оба ключа одновременно замкнуты (рис.

4.3). ’ Иначе результат умножения

равен нулю.

Закон для операции логического сложения ИЛИ изображен на рИС 4 4. Для

логического сложения ключи в схеме рис. 4.4 включены параллельно. На

выходе будет логическая 1 тогда, когда хотя бы один ключ находится в

состоянии 1.

В логическом элементе НЕ единица на входе превращается в 0 на выходе, а 1 на входе — в 0 на выходе (рис. 4.5).

Похожие статьи