Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Логические элементы на КМОП-транзисторах

Сокращение КМОП означает «комплементарный

МОП-транзистор». Также иногда используется сокращение COSMOS,

которое обозначает «комплементарная симметричная

МОП-структура». Логические элементы этого подсемейства строятся

как на «-канальных МОП-полевых транзисторах, так и на

/^-канальных МОП-полевых транзисторах. Схемы этого подсемейства

характеризуются ярко выраженной симметрией. При разработке схем

применяют только самозапирающиеся МОП-транзисторы (см. Бойт,

Электроника, ч. 2, разд. 8.2, МОП-полевые транзисторы).

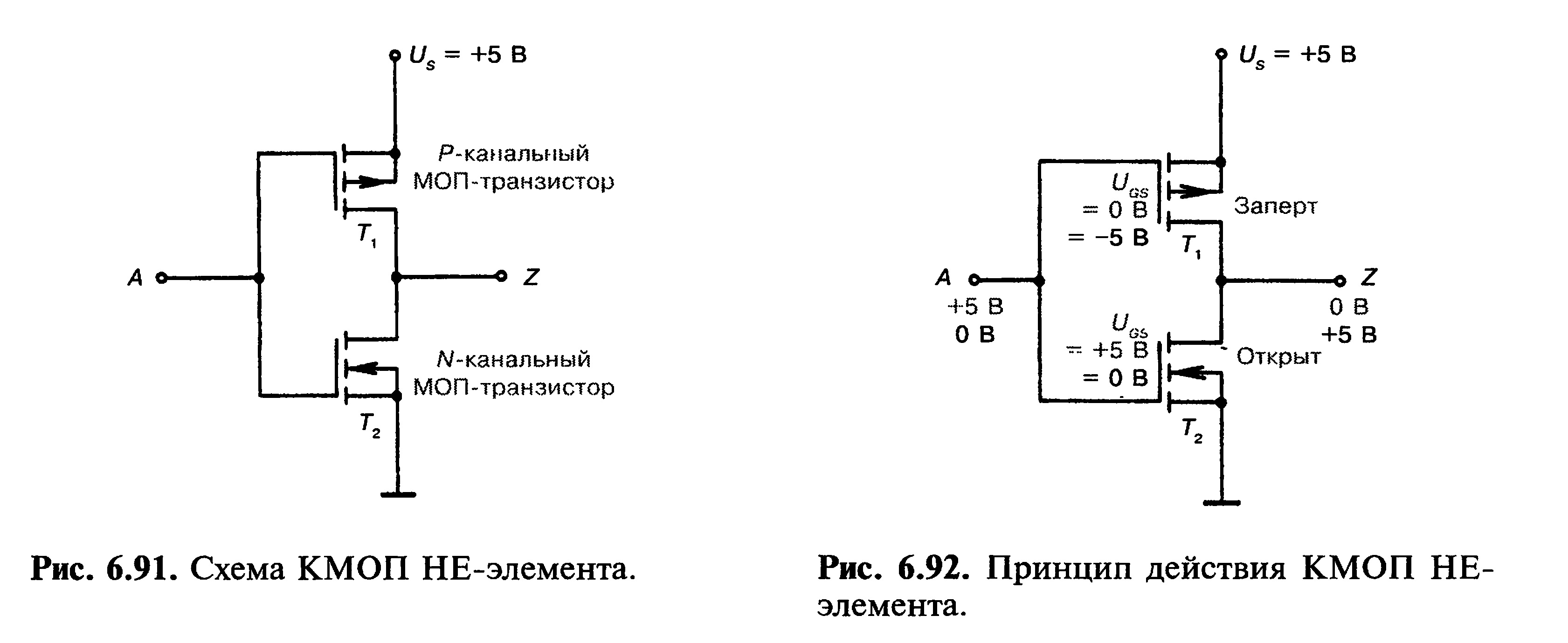

Симметричность схем видна особенно хорошо в схеме элемента НЕ (рис.

6.91). Если на входе А действует Я-уровень, например +5 В, то

транзистор Т2 отпирается. На его истоке и подложке 0 В. Напряжение

затвор-исток UGS составляет +5 В. К истоку и подложке транзистора Тх

приложены +5 В.

Если к управляющему электроду также прикладываются +5 В, то

напряжение затвор-исток UGS = О В. Транзистор Тх заперт. Если Тх

заперт, а Т2 открыт, то выход элемента Z имеет уровень L (рис. 6.92).

Если на входе А действует i-уровень О В, то транзистор Т2 запирается и

напряжение затвор-исток UGS составляет О В. Напряжение затвор-исток

транзистора Ту UGS = —5 В, так как напряжение истока +5 В, а

затвора О В. Транзистор отпирается. Если Тх открыт, а Т2 заперт, выход

элемента Z имеет уровень Н.

В КМОП-НЕ-элементе всегда один транзистор открыт, а другой заперт.

Если на выходе элемента НЕ действует уровень 0, то элемент практически

не потребляет ток, так как Тх заперт. Если на выходе элемента НЕ

действует уровень Н, то элемент также практически не потребляет ток,

так как теперь Т2 заперт. Для управления последовательно включенными

элементами также не требуется ток, так как полевые транзисторы

практически не потребляют мощность. Только во время переключения от

источника питания потребляется небольшой ток, так как оба транзистора

одновременно, но недолго открыты. Один из транзисторов переходит из

открытого состояния в запертое и еще не полностью заперт, а другой

— из запертого в открытое и еще не полностью открыт. Также должны

перезарядиться транзисторные емкости.

Все КМОП-элементы устроены так, что в токовой ветви один транзистор

закрыт, а другой открыт. Энергопотребление КМОП-элементов крайне низко.

Оно зависит в основном от количества переключений в секунду или частоты

переключения.

КМОП-элементы отличаются малым энергопотреблением.

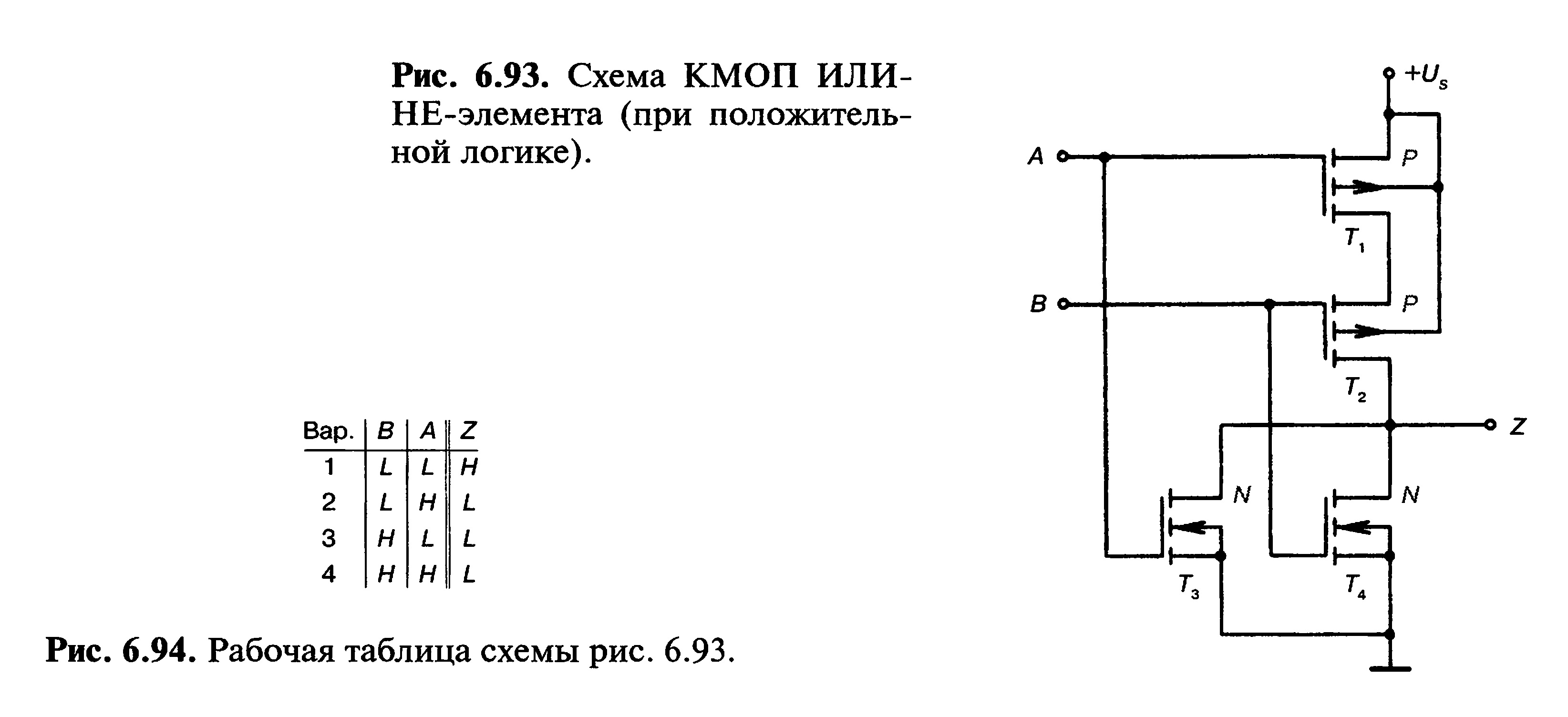

На рис. 6.93 изображена следующая типичная КМОП-схема. Если на обоих

входах действует уровень L, то транзисторы 7’ и Т2 будут открыты,

транзисторы Тг и Т4 заперты. Ту и Т2 при О В на А и В имеют UGS =

— 5 В, а Т3 и Т4 имеют UGS = О В. На выходе Z действует уровень Н.

Если на входе А действует уровень Н(+5 В), а на входе 5-уровень L (О

В), то Ту закрывается, а Т2 открывается. Путь от источника питания к

выходу Z блокирован запертым транзистором.

Одновременно отпирается транзистор Т3 и на выходе Z действует

примерно О В, то есть уровень L. Г4 заперт. Z всегда имеет уровень Z,

если по крайней мере на одном входе действует уровень Н.

Соответствующая схеме (рис. 6.93) рабочая таблица представлена на рис.

6.94. Схема производит при положительной логике операцию ИЛИ-НЕ.

Какую логическую операцию производит схема на рис. 6.95? Прежде всего

для схемы должна быть составлена рабочая таблица. Если на обоих входах

действуют Z-уровни (О В), то транзисторы Т{ и Т2 открываются (UGS =

— 5 В). Транзисторы Т3 и Г4 закрываются (UGS = О В). На выходе

Л-уровень.

Если на обоих входах действуют #-уровни (+5 В), то транзисторы Тъ и Т4

открываются, а транзисторы Тх и Т2 закрываются. На выходе Z будет

действовать Z-уровень.

Если на один вход приложен Я-уровень, а на другой — Z-уровень, то

один из верхних транзисторов на рис. 6.95 (7^ или Т2) открывается. Один

из нижних (Т3 или Г4) запирается. Через открытые транзисторы к выходу

будет прикладываться if-уровень. На рис. 6.96 представлена

соответствующая таблица истинности. Схема выполняет при положительной

логике функцию И-НЕ.

КМОП-элементы производятся в основном в виде элементов И-НЕ и ИЛИ-НЕ.

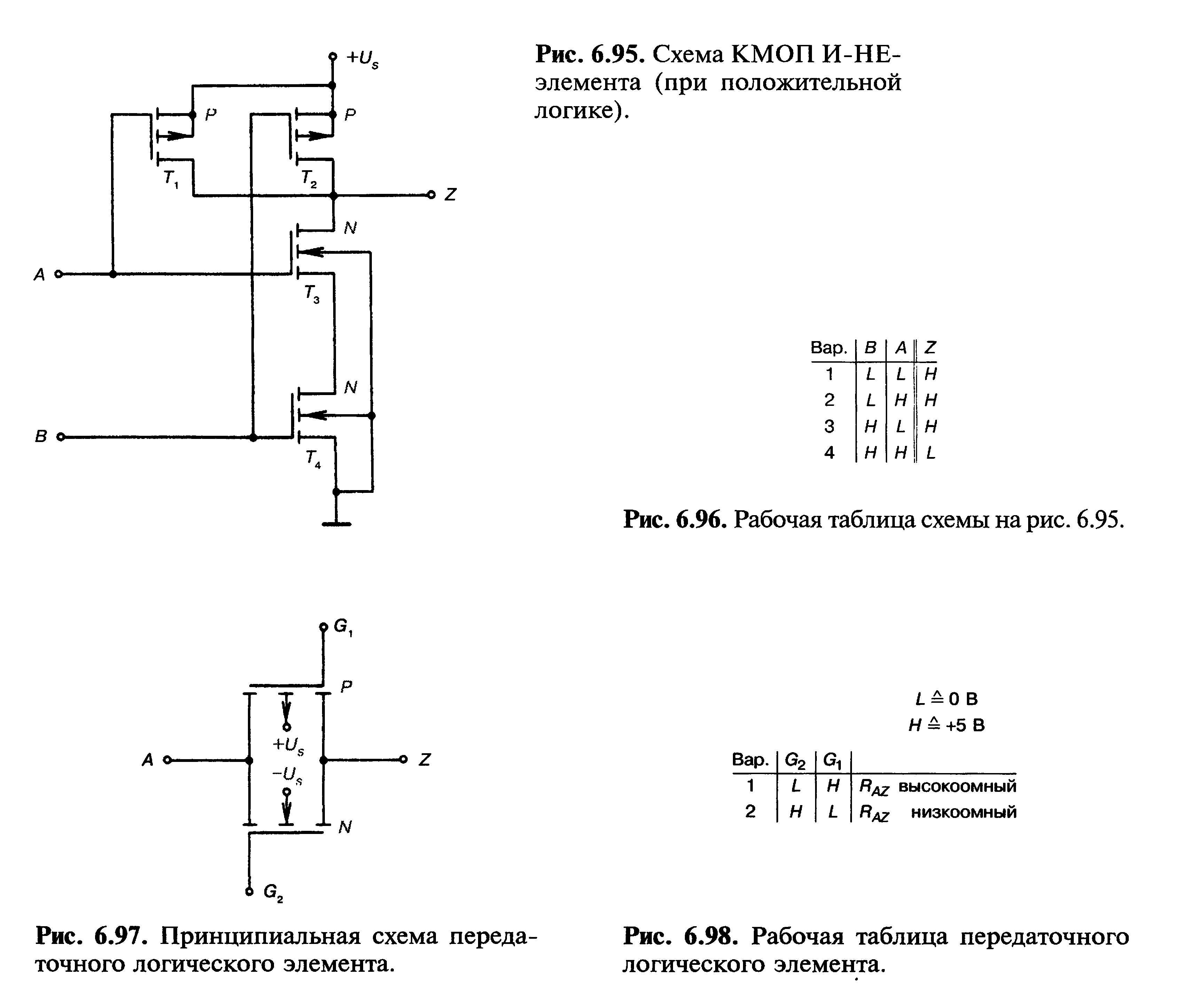

Особым элементом подсемейства КМОП является передаточный элемент. Он

состоит из параллельного включенных и-канального МОП-транзистора и

^-канального МОП-транзистора (рис. 6.97).

Передаточный элемент работает как переключатель.

Если к Gx будет приложен уровень Н (например +5 В) и к G2 —

уровень L (О В), то оба транзистора запираются. В /ьканальном

МОП-транзисторе между управляющим электродом и подложкой приложено

напряжение О В. Образование проводящего канала между истоком и стоком

становится невозможным. Также и в я-канальном МОП-транзисторе между

управляющим электродом и подложкой приложено напряжение О В. Здесь

также не может возникнуть проводящий канал. Сопротивление между точками

А и Zдостигает нескольких сотен МОм.

Если на <7, действует уровень L (О В), а на G2 — уровень Н (+5

В), то напряжение затвора /^-канального МОП-транзистора относительно

подложки будет —5 В. Напряжение затвора и-канального

МОП-транзистора относительно подложки +5 В. При этих напряжениях

образуются проводящие каналы между истоком и стоком. Канал между А и Z

будет низкоомным (примерно от 200 Ом до 400 Ом). Рабочая таблица

представлена на рис. 6.98.

Уровни на входах Gl и G2 всегда прикладываются в противофазе.

Управление может происходить с помощью элемента НЕ (рис. 6.99).

Получается двунаправленный ключ. У полевых транзисторов передаточного

элемента исток и сток могут взаимно менять свои функции. Поэтому вывод

затвора обозначается в середине его условной линии (рис. 6.99).

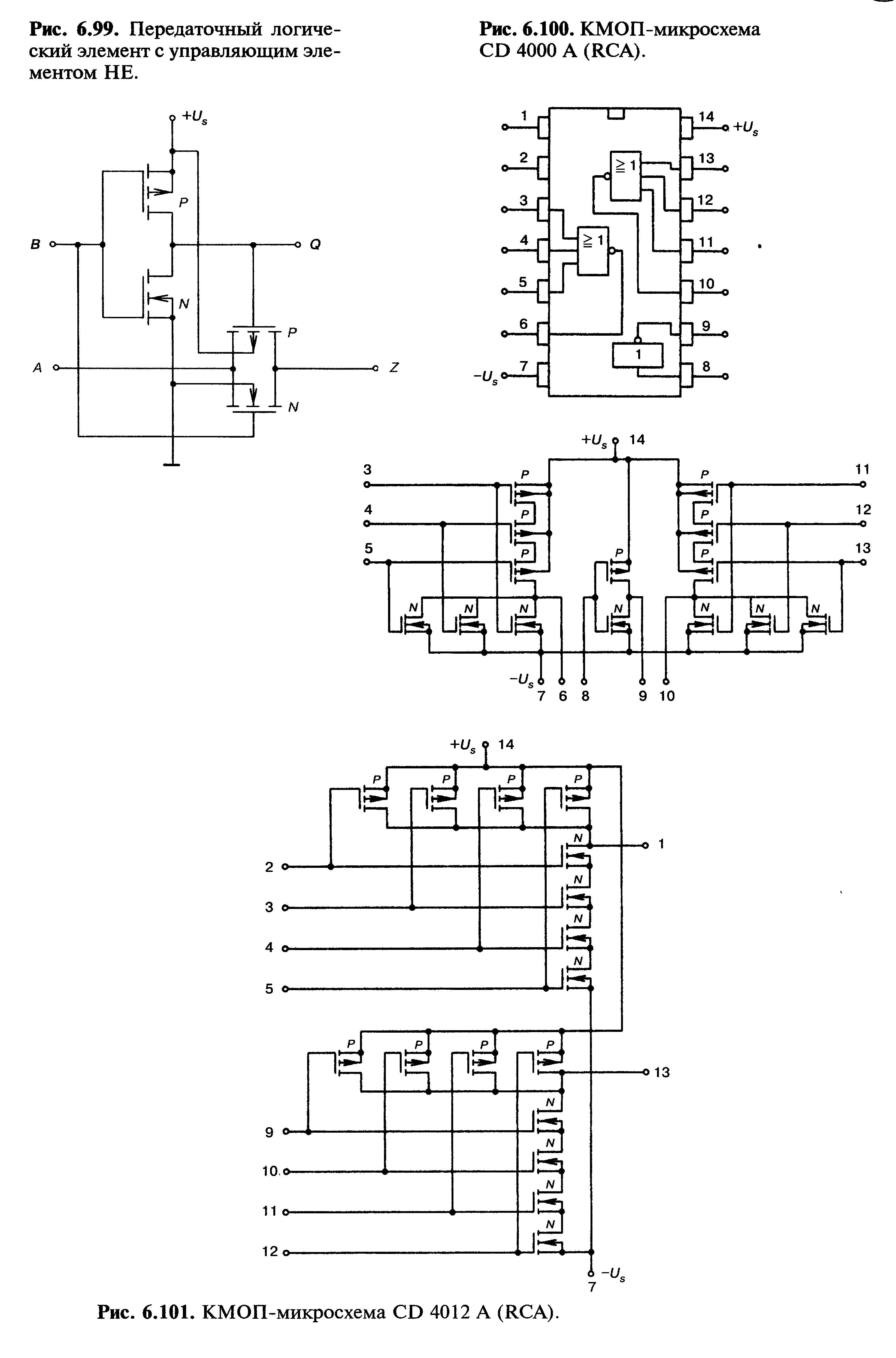

Интегрированные КМОП-микросхемы всегда содержат множество логических

элементов, которые могут быть использованы по отдельности или как

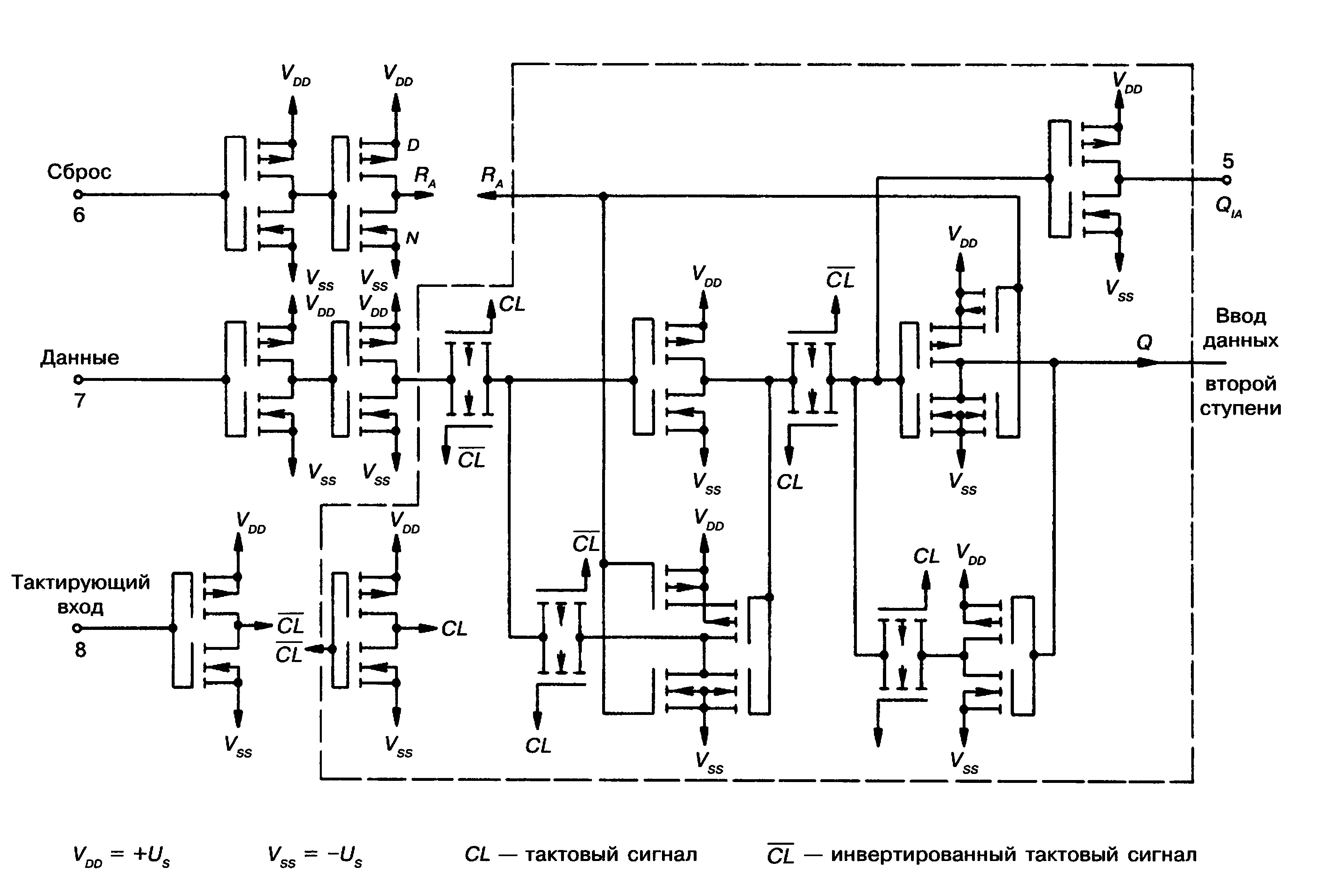

единая сложная логическая функция. На рис. 6.100 показана структура

схемы CD 4000 А. Эта схема содержит два элемента ИЛИ-HE с тремя входами

каждый и элемент НЕ. Схема CD 4012 А (рис. 6.101) содержит два элемента

И-НЕ с четырьмя входами каждый.

Интегральные схемы арифметических логических устройств содержат очень

много КМОП-элементов. На рис. 6.102 приведена схема 4-битного

сдвигающего регистра. Эта схема рассмотрена подробно в гл. 8.

Рис. 6.102. Схема КМОП-4-битного сдвигового регистра CD 4015 A (RCA)

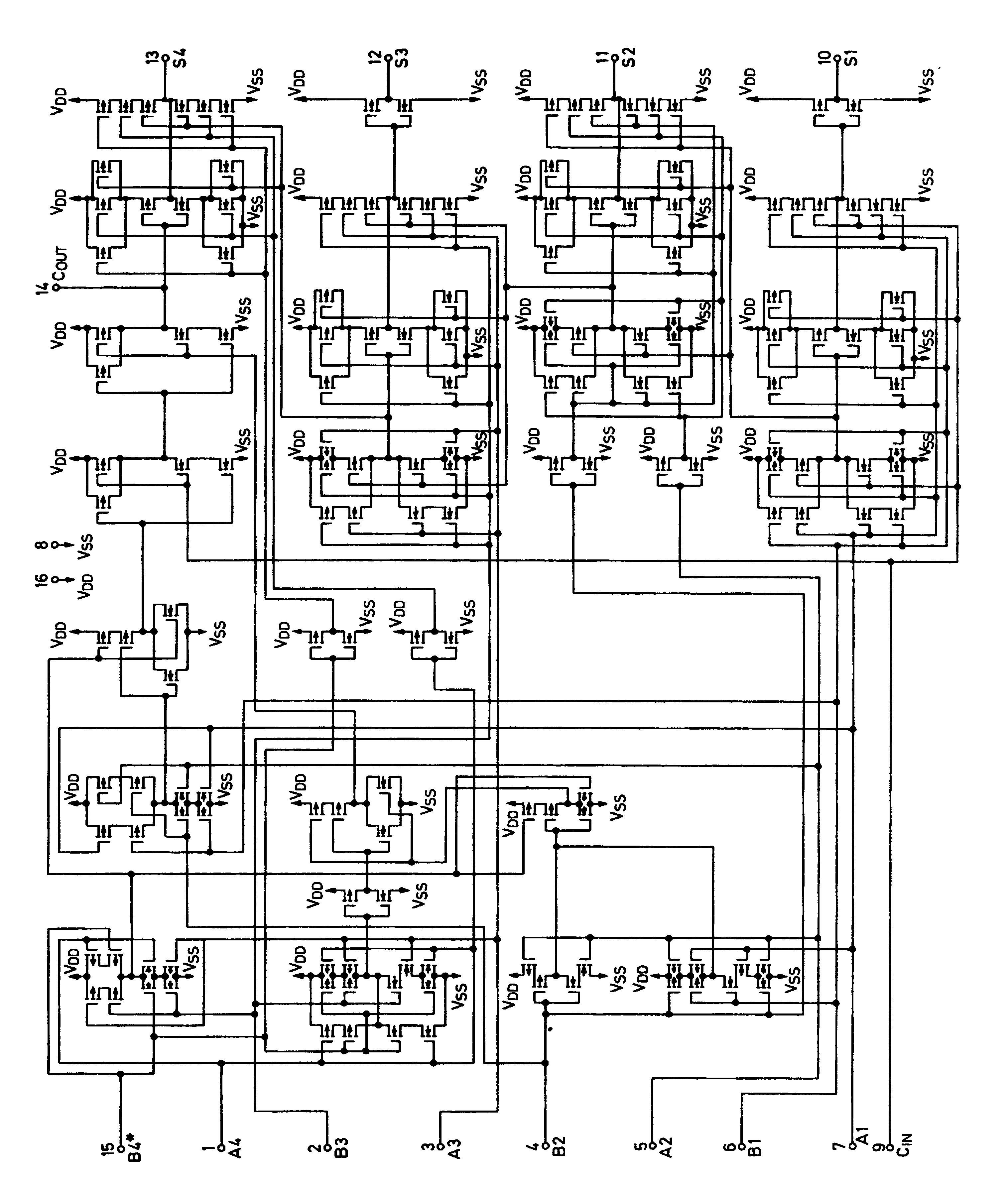

Микросхема CD 4008 А является 4-битным полным сумматором. Полные

сумматоры рассматриваются подробно в гл. 10. Схема приведена здесь как

пример КМОП-схемотехники (рис. 6.103).

Интегральные микросхемы в КМОП-исполнении могут производиться с очень большой плотностью элементов,

Можно схему целого калькулятора уместить в одной микросхеме. Дальнейшее

совершенствование технологий ведет к повышению возможной плотности

компоновки.

Напряжение питания КМОП-элементов может колебаться в широком диапазоне.

Для серии CD-4000-A (рис. 6.100—6.103) фирма-производитель RCA

указывает диапазон напряжений питания от 3 В до 15 В. Типичные

передаточные характеристики при ряде напряжений питания показаны на

рис. 6.104.

Часто используются напряжения питания +5 В и +10 В. Для этих напряжений

питания на рис. 6.105 и 6.106 показаны диаграммы уровней. Для больших

напряжений питания характерна лучшая помехоустойчивость.

Разность между уровнями L и Н, отвечающая за помехоустойчивость, для

КМОП-схем составляет примерно от 30% до 40% напряжения питания.

В следующей таблице приведены важнейшие параметры КМОП-эле-ментов:

Рис. 6.103. Схема КМОП-4-битного полного сумматора CD 4008 A (RCA)

Похожие статьи