Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Шотки-ТТЛ (ТТЛШ)

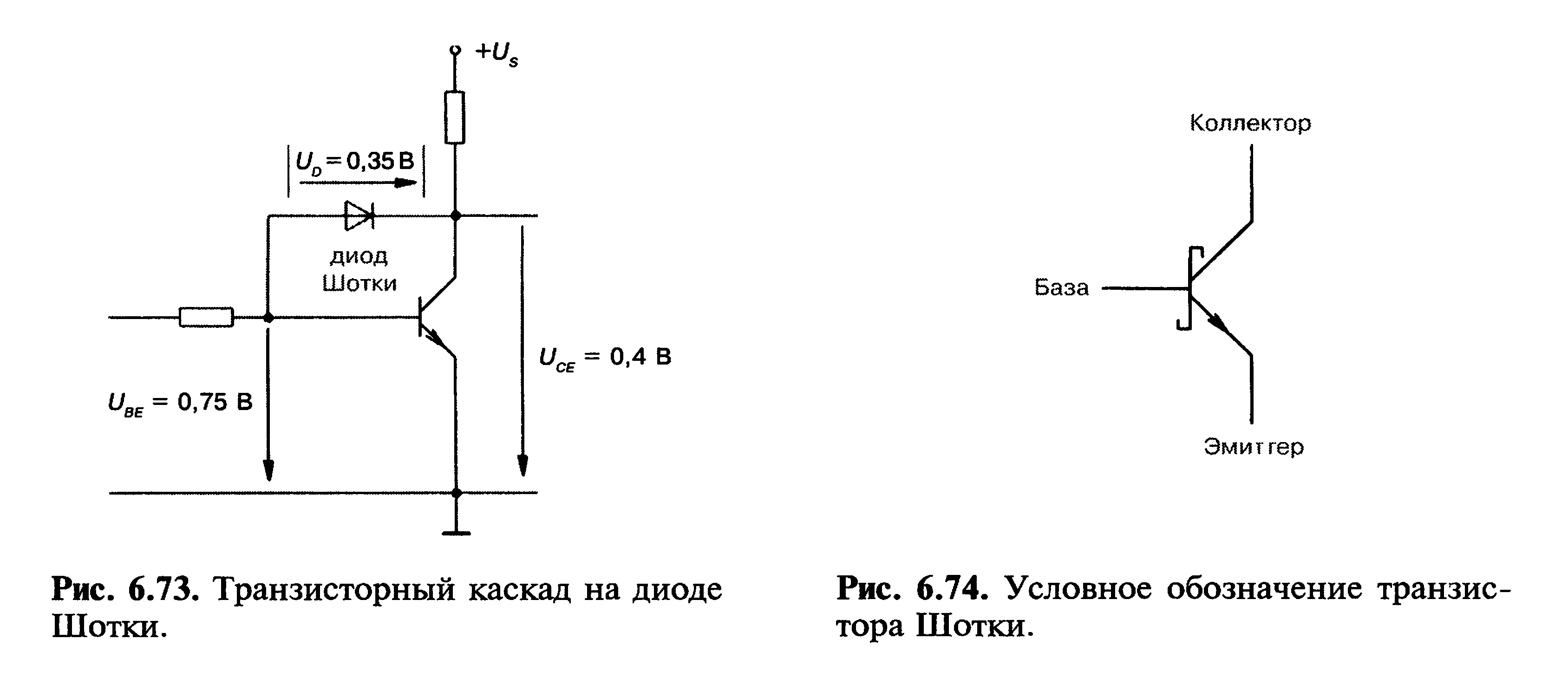

При создании одновременно быстрых и экономичных микросхем

используется свойство транзисторов быстро переключаться в ненасыщенном

состоянии (см. Бойт/Шмуш, Электроника, ч. 3). При подключении диода по

рис. 6.73 предотвращается насыщение транзистора. Диод должен иметь

высокое быстродействие. Поэтому применяют диоды Шотки (см. Бойт,

Электроника, ч. 2). Диоды Шотки отличаются высоким быстродействием и

пороговым напряжением 0,35 В.

Транзистор на рис. 6.73 может проводить только до тех пор, пока UCE не

упадет до 0,4 В. Затем диод Шотки предотвращает дальнейшее нахождение

транзистора в открытом состоянии. Он сам проводит в прямом направлении.

От базы ток течет через диод и переход коллектор-эмиттер к земле. Этот

ток уже не течет через базу транзистора и не служит для его управления.

Начало насыщения транзистора начинается тогда, когда UCE падает до

значения UBE, т. е. при UCE = 0,4 В транзистор уже находится в

насыщении, но не в глубоком.

Диод Шотки на рис. 6.73 называется «антинасыщающий диод».

Транзистор с диодом Шотки называется транзистором Шотки. Его условное

обозначение показано на рис. 6.74. Диод при этом подразумевается по

умолчанию, и его можно не обозначать на схеме.

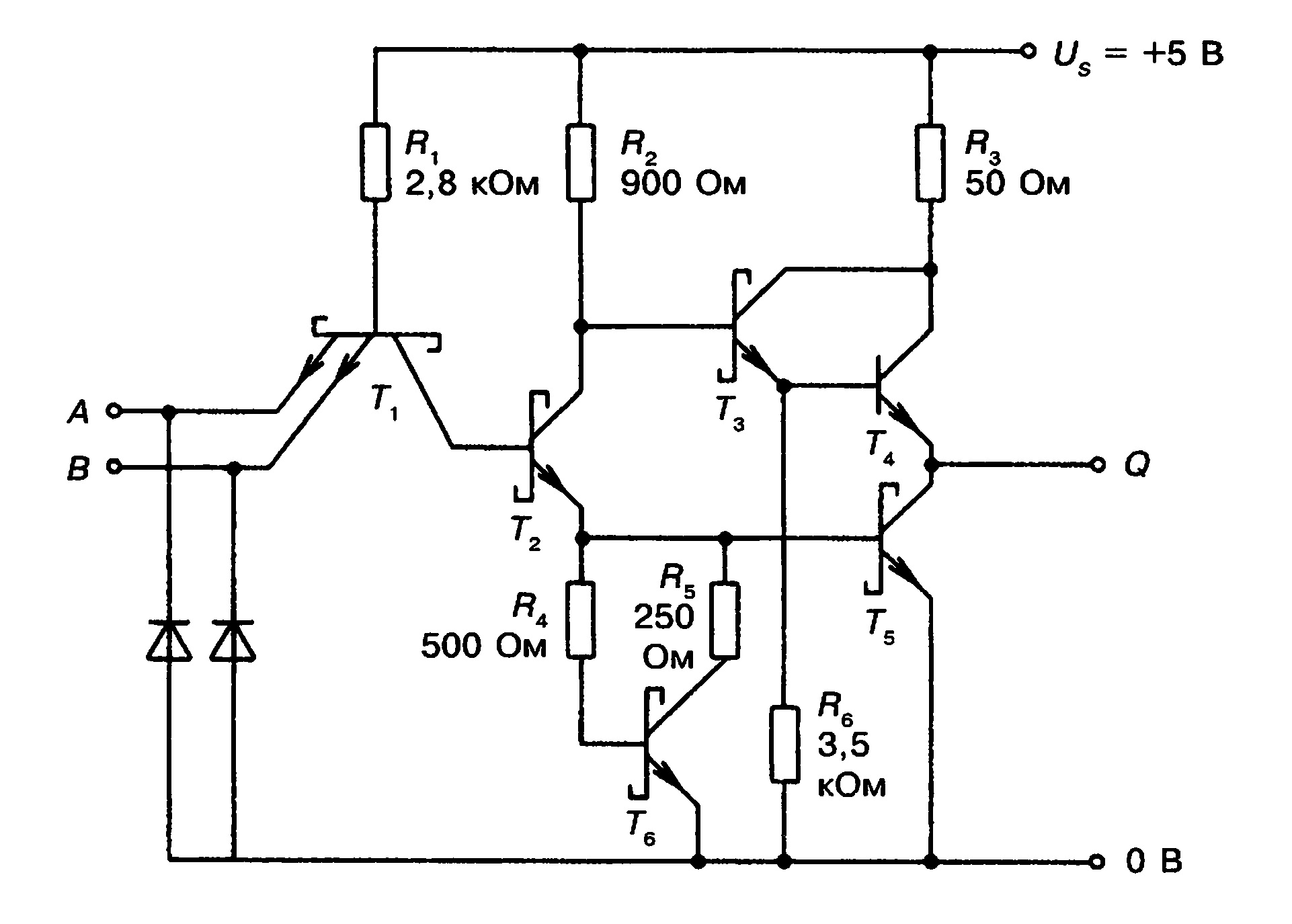

Принципиальная схема типичного элемента ТТЛШ изображена на рис. 6.75. Это элемент И-НЕ в положительной логике.

Среднее время задержки tp составляет от 2,5 до 3 не, или примерно

вдвое меньше, чем для элементов подсемейства высокоскоростных ТТЛ.

Так как транзисторы Шотки проводят слабо, выходной уровень L у них

выше, чем у стандартных ТТЛ-элементов. Вследствие этого разрыв между

уровнями L и Н меньше, что означает ухудшение статической

помехоустойчивости.

Логические элементы подсемейства ТТЛШ характеризуются очень высоким

быстродействием, плохой помехоустойчивостью и высоким

энергопотреблением.

Элемент И-НЕ (рис. 6.75) потребляет мощность 20 мВт — вдвое больше, чем элемент И-НЕ подсемейства стандартных ТТЛ.

Рис. 6.75. Элемент ТТЛШ 74 S 00 (Texas Instruments)

Похожие статьи