Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Дополнительные триггерные схемы

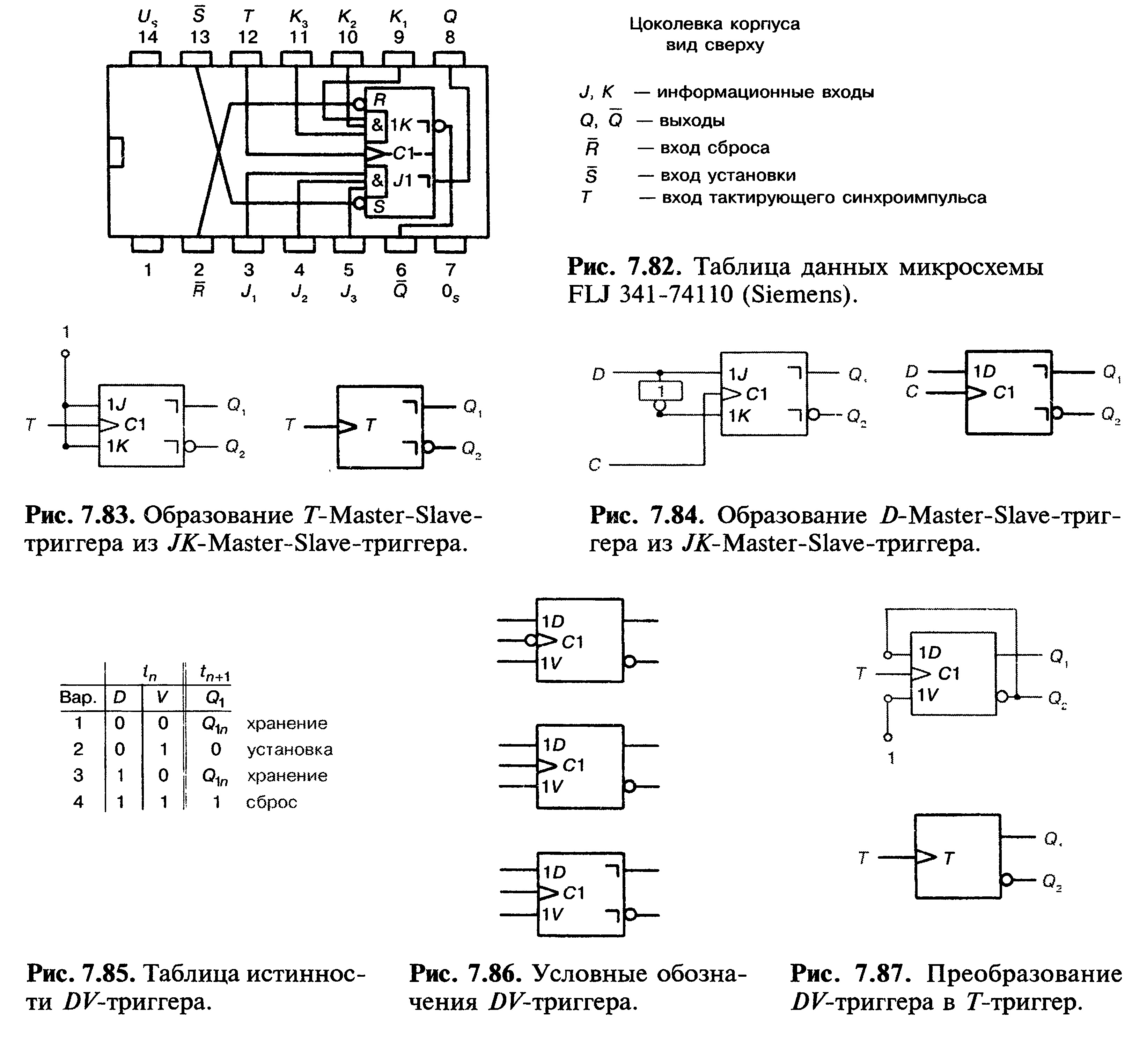

Число возможных триггерных схем чрезвычайно большое. Уже обсужденные /^-триггеры и Г-триггеры также производятся как MS'-триггеры, или как управляемые по двум фронтам триггеры. Их можно также построить на базе /if-MASTER-SLAVE-триггеров.

К входам /AT-MASTER-SLAVE-триггера на рис. 7.83 прикладывается 1-уровень, т. е. напряжение питания. Триггер будет переключаться на каждом такте. Такая схема называется r-MASTER-SLAVE-триггер и является идеальной для построения асинхронных счетчиков (гл. 11).

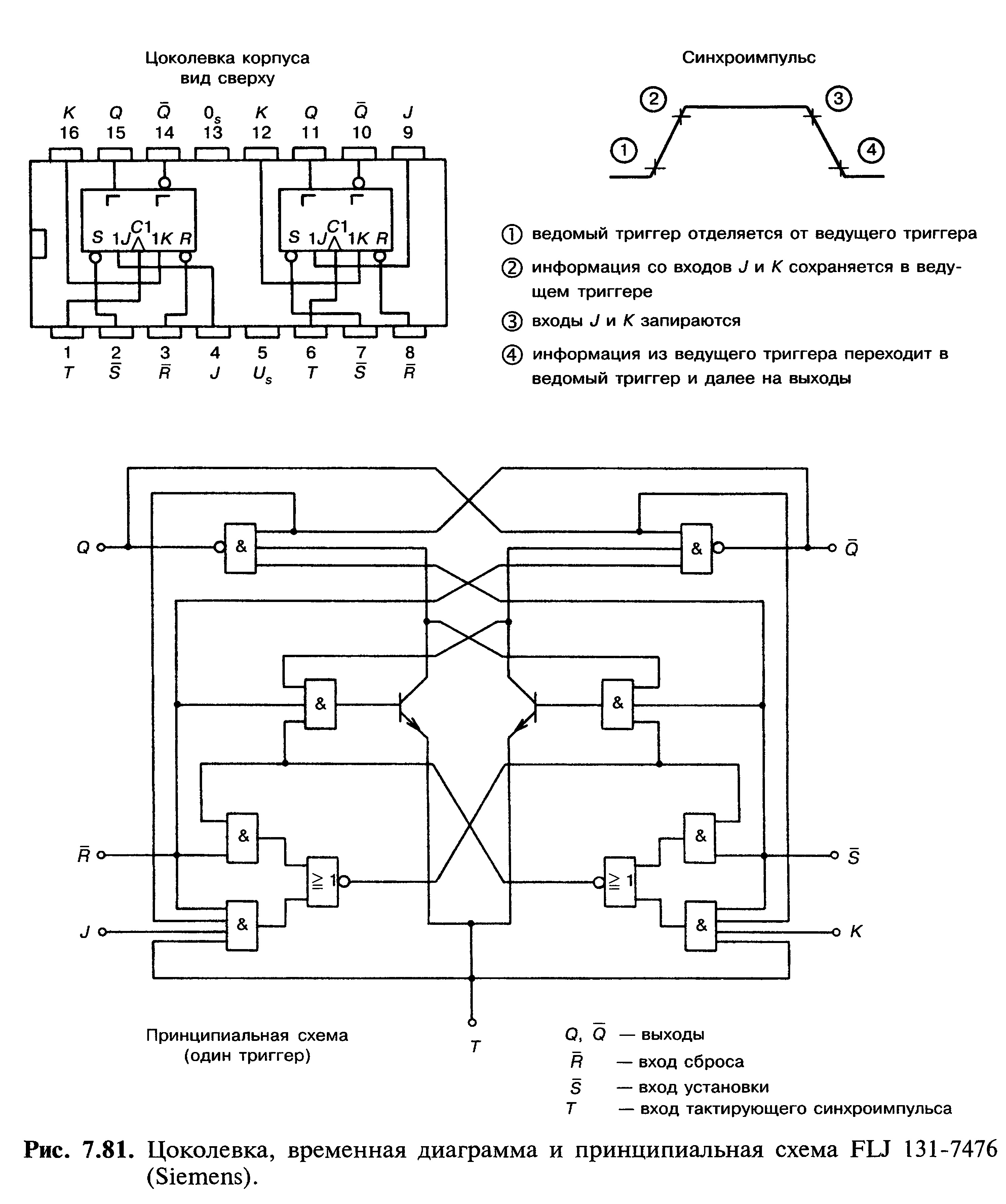

Рис. 7.81. Цоколевка, временная диаграмма и принципиальная схема FLJ 131-7476 (Siemens)

D-MASTER-SLAVE-триггер очень легко построить на базе Ж-MASTER-SLAVE-триггера (рис. 7.84).

Следующим интересным триггером является DK-триггер. Таблица истинности для Z)F-триггера приведена на рис. 7.85. Триггер работает как D-триггер, если на подготовительном входе V действует 1-сигнал. Он заперт, т. е. состояния выходов не меняются, если на подготовительном входе Vдействует 0-сигнал.

Условное обозначение DF-триггера показано на рис. 7.86. DV-триггер можно приобрести в виде управляемого по одному фронту триггера или в виде управляемого по двум фронтам MS'-триггера. Он может быть легко преобразован в Г-триггер (рис. 7.87).

Ведущий Ж-триггер с блокированием входа

Модуль FLJ 341 /345 имеет время промежуточного хранения всего 5 не относительно переднего фронта синхроимпульса. Это значит, что Ж-сигналы могут меняться уже во время синхронизирующего импульса без вызывания ложного срабатывания. FLJ 341/345 взаимозаменяем с FLJ 111/115.

Похожие статьи