Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Не тактируемые триггеры

Триггер на элементах «ИЛИ-НЕ»

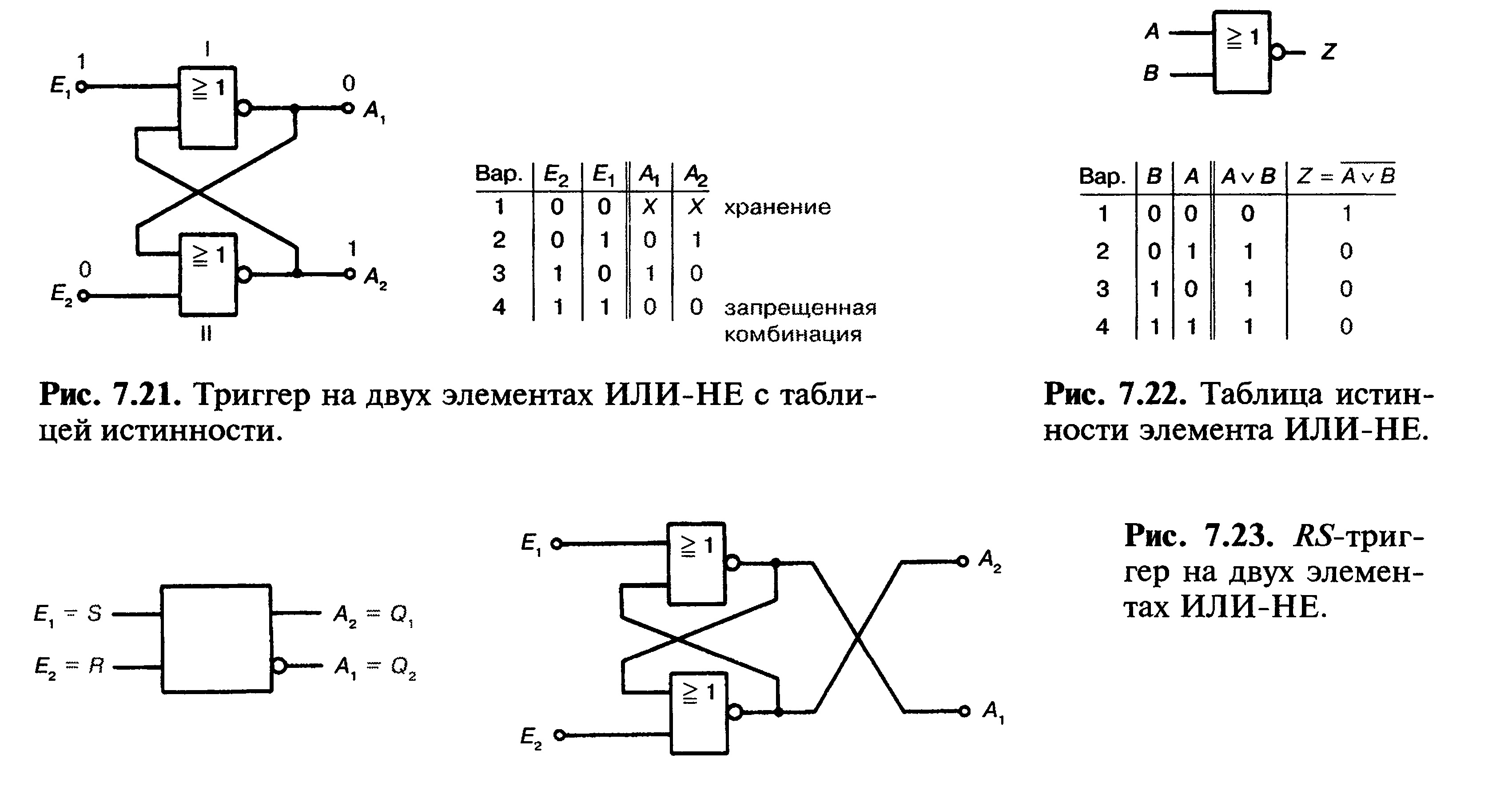

Простой нетактируемый триггер может быть построен на двух логических элементах ИЛИ-HE (рис. 7.21). Выход элемента ИЛИ-HE находится в нулевом состоянии, если по меньшей мере на одном из входов присутствует 1 (рис. 7.22). Если к Ех прикладывается 1, то Ах переходит в 0. На входе Е2 должен быть 0. Тогда на обоих входах элемента ИЛИ-HE //присутствует 0. Выход А1 перейдет в 1 состояние (вар. 2 таблицы истинности на рис. 7.21).

В случае 3 таблицы истинности (Ех = 0, Ег = 1) на А2 установится 0, а Ах переходит в 0.

Если на обоих входах действует 0, то состояние выходов триггера остается неизменным. Можно перейти от варианта 2 к варианту 1 или от варианта 3 к варианту 1. Состояния сигналов варианта 2 изображены серым на рис. 7.21. Если Ej устанавливается в 0, то выходы не меняют своих состояний. Такой режим называется «режим хранения».

Если на обоих входах действует 1, то оба выхода должны перейти в 0. Теперь выходы не имеют противоположных состояний. Режим, соответствующий сигналам Ех = 1, Е2 = 1 является так называемым запрещенным режимом. Он никогда не используется.

Рис. 7.23. RS-триггер на двух элементах "ИЛИ-НЕ"

Согласно правилам для триггеров 1 на Ег должна устанавливать в 1 противоположный выход. То есть 1 на Е2 в данном случае должна установить в 1 нижний выход. Это достигается путем перестановки выходов согласно рис. 7.23. Так как А2 относится к верхнему, а А{ — к нижнему выходам, то выходы переставляются местами:

А2 = Q-, Ах = Q2

Вход Еу является входом установки. Он обозначается символом S. Вход R является сбросом. Он обозначается символом R. Триггер на рис. 7.23 называется ЛУ-триггер.

Похожие статьи