Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Моностабильные ячейки

Моностабильные ячейки имеют два состояния. Одно из них называется стабильным состоянием.

В стабильном состоянии на основном выходе G действует 0-сигнал.

Стабильное состояние устанавливается после подачи напряжения питания. Оно сохраняется до тех пор, пока ячейка не перейдет при поступлении управляющего сигнала на вход в нестабильное состояние.

В нестабильном состоянии на основном выходе О действует 1-сигнал.

Длительность нахождения в нестабильном состоянии определяется внешними элементами. В основном это конденсаторы (Сг) и сопротивления (RT). Время нахождения в нестабильном состоянии определяется уравнением:

tQ =0,69 RT СТ

tQ — время нахождения в нестабильном состоянии.

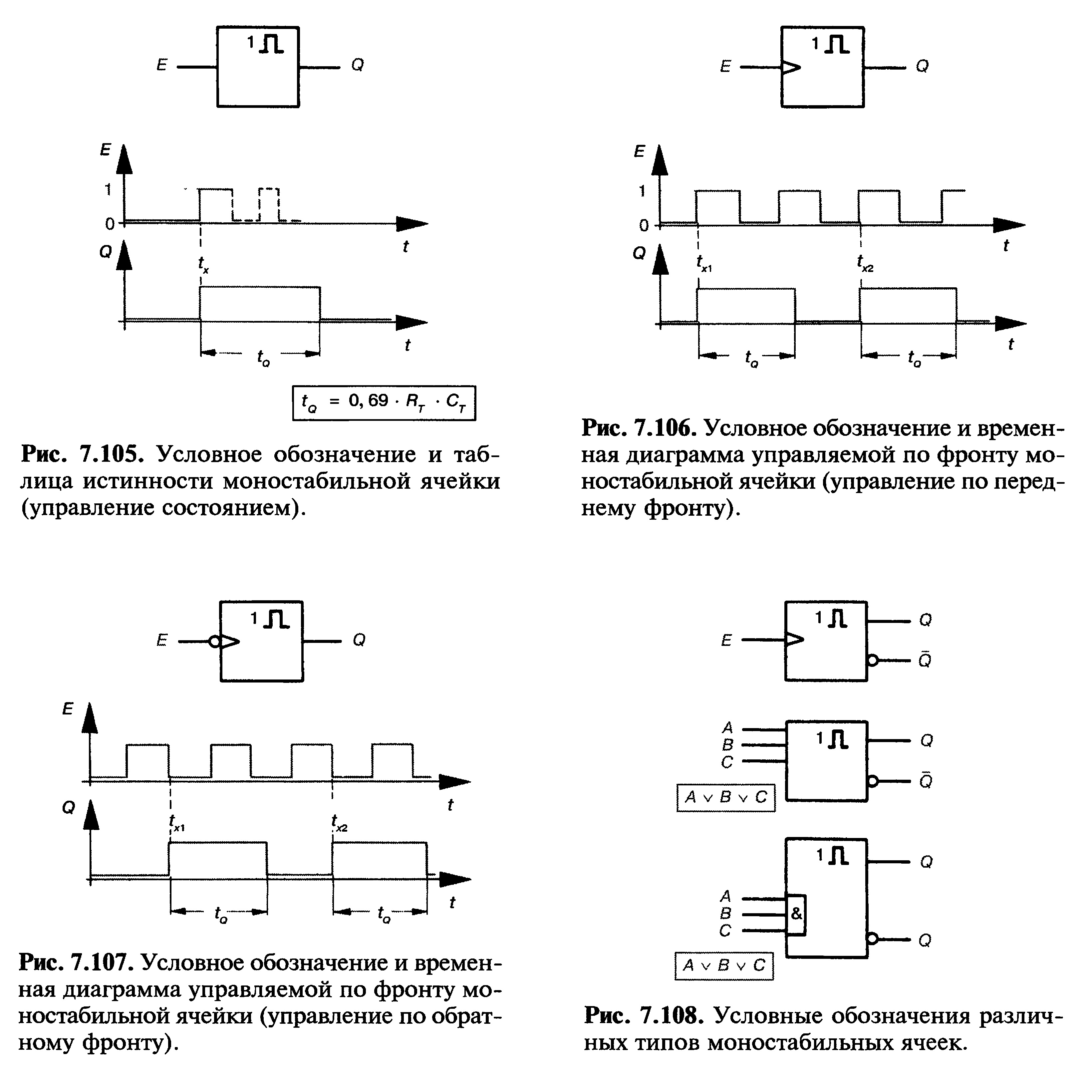

Структура бистабильных ячеек рассмотрена в книге «Электроника», ч. 3 (Бойт/Шмуш), разд. 7.2. Бистабильные ячейки производятся в большом количестве в виде интегральных микросхем, в основном ТТЛ-семейства. На рис. 7.105 показано условное обозначение и временная диаграмма мо-ностабильной ячейки. В момент времени tx на входе появляется 1-сигнал. Ячейка переключается в Q = 1. По истечении времени tQ она самостоятельно возвращается обратно в стабильное состояние.

Изменение входного сигнала в течение времени нахождения в нестабильном состоянии tQ не оказывает влияния на состояние моностабильной ячейки.

Если в течение времени tQ входной сигнал изменяет свое состояние с 0 на 1, то время нахождения в нестабильном состоянии не увеличивается.

Моностабильные ячейки управляются фронтально-тактовым способом. Они меняют состояние либо по переднему, либо по заднему фронту импульса входного сигнала.

На рис. 7.106 представлены условное обозначение и временная диаграмма моностабильной ячейки, которая переключается передним фронтом импульса входного сигнала. Ячейка переключается в момент времени txv В течение времени tQ она находится в нестабильном состоянии. Изменения входного сигнала в это время не влияют на состояние выхода. Возврат в стабильное состояние происходит и тогда, когда на входе присутствует 1-сигнал. Моностабильная ячейка переключается опять в точке tn.

На рис. 7.107 показаны условное обозначение и временная диаграмма управляемой по фронту моностабильной ячейки, переключаемой задним фронтом импульса.

Моностабильные ячейки могут иметь несколько выходов. Они обозначаются, как показано на рис. 7.108. Наряду с основным выходом Q имеется

выход Q, состояние которого всегда противоположно состоянию выхода Q. Также возможны несколько входов. Эти входы связаны друг с другом логическим сложением ИЛИ, если нет указания на какую-либо другую связь. При логическом умножении И-входы объединяются знаком логического умножения, как показано на рис. 7.108.

Время нахождения в нестабильном состоянии tQ может указываться на условном обозначении моностабильной ячейки. Согласно DIN 40700, ч. 14, могут использоваться заглавные буквы для единиц времени, то есть S для секунд, MS для миллисекунд и NS для наносекунд (рис. 7.109).

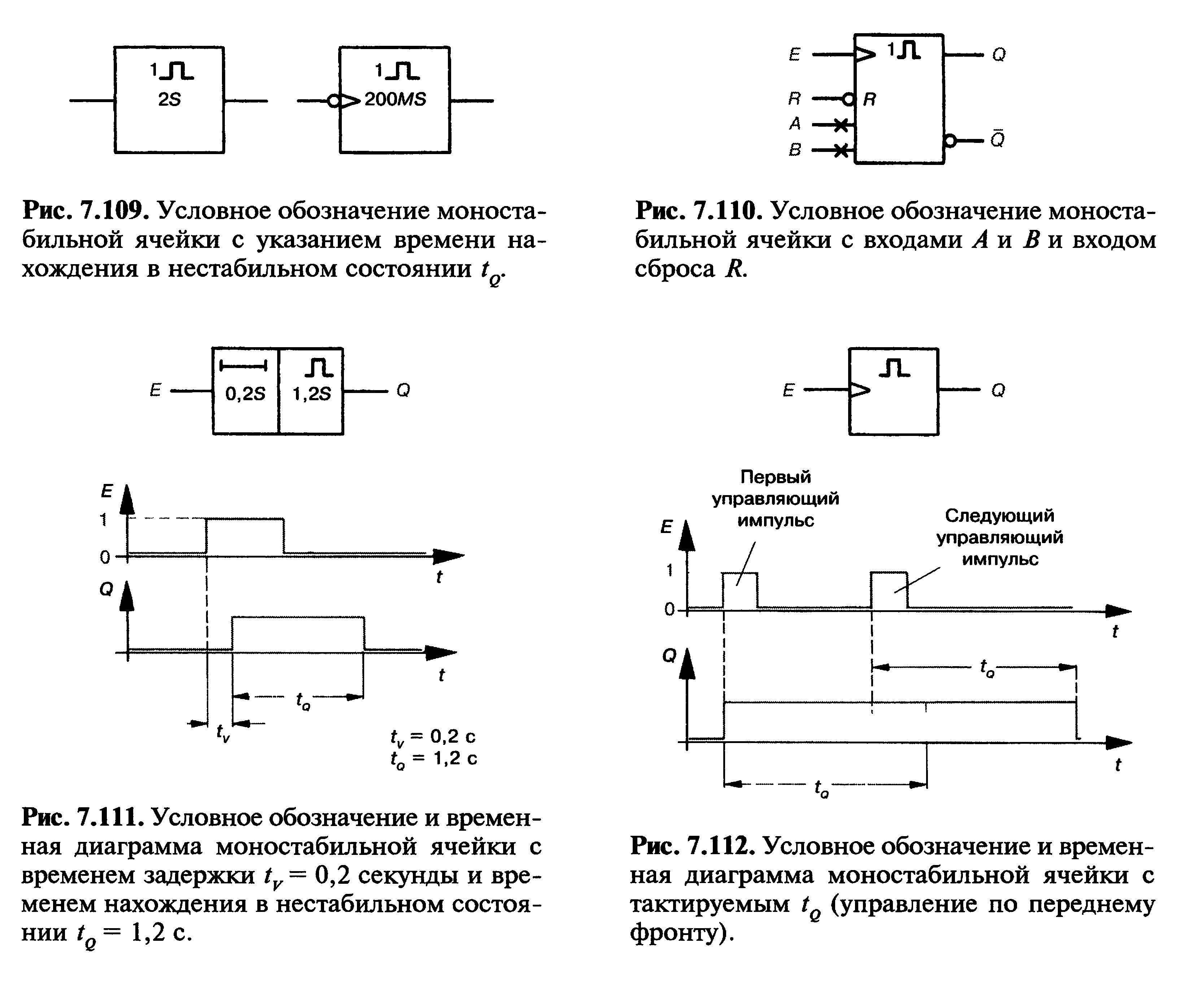

Время tQ определяется в основном внешними элементами. Входы микросхемы, к которым подключаются эти внешние элементы, обозначаются крестами. Рис. 7.110 показывает условное обозначение моностабильной ячейки с управляющим входом Е, входом сброса R и входами А и В, к которым подключаются внешние элементы. 0-сигнал на R возвращает ячейку в Q = 0 (возврат в стабильное состояние). Управление происходит передним фронтом синхроимпульса. Моностабильные ячейки могут быть построены так, чтобы срабатывать с задержкой. Для таких ячеек используется условное обозначение (рис. 7.111). Время задержки может указываться в условном обозначении.

На рис. 7.111 оно составляет tv= 0,2 с. Наряду с рассмотренной моностабильной ячейкой существует как частный случай моностабильная ячейка с тактируемым временем нахождения в нестабильном состоянии.

В моностабильных ячейках с тактируемым временем нахождения в нестабильном состоянии tQ регулируется и может быть увеличено посредством управляющих импульсов.

После переключения такой ячейки в нестабильное состояние начинается отсчет tQ. Если в течение этого времени поступает новый управляющий импульс, то отсчет времени tQ начинается сначала. Следующий управляющий импульс снова начинает отсчет tQ сначала и так далее. На рис. 7.112 представлена временная диаграмма моностабильной ячейки с тактируемым временем нахождения в нестабильном состоянии.

Условное обозначение для моностабильной ячейки с тактируемым временем нахождения в нестабильном состоянии введено в DIN 40900, ч. 12. Оно совпадает с условным обозначением для обычной моностабильной ячейки, только 1 перед знаком импульса убирается (рис. 7.112). Ранее употребляемая буква N больше не пишется.

Производители интегральных микросхем предлагают различные моностабильные ячейки. В качестве примера приведем только одну схему. Интегральная микросхема FLK 101-74 121 построена согласно рис. 7.113. Она содержит элемент ИЛИ с инверсными входами. Через элемент И управляется моностабильная ячейка, которая переключается передним фронтом синхроимпульса. Вход В является входом триггера Шмитта. Через этот вход можно работать с медленно возрастающими сигналами (примерно до 1 В/с).

Если на одном из Л-входов сигнал меняется с 1 на 0, то выходной сигнал элемента ИЛИ переходит с 0 на 1. Если ко входу В приложен сигнал 1, то выходной сигнал элемента И переключается с 0 на 1. Моностабильная ячейка переходит в нестабильное состояние. Если В = 1, то моностабильная ячейка управляется задним фронтом импульса на входах А. Если 5 = 0, то изменения сигнала на A-входах не оказывают воздействия.

Если управление осуществляется с 5-входа, то на одном из входов А должен быть нулевой сигнал. На выходе элемента ИЛИ тогда действует 1. Начинаем медленно увеличивать сигнал на входе В. Когда его величина будет больше порогового значения триггера Шмитта, выходной сигнал триггера изменится с 0 на 1. Тогда выходной сигнал элемента «И» изменится с 0 на 1, и моностабильная ячейка переключится в нестабильное состояние.

Элементами, определяющими время нахождения в нестабильном состоянии tQ, являются сопротивление RT и конденсатор Сг Конденсатор подключен к выводам 10 и 11 (положительный полюс на 11). Сопротивление подключено к выводам 11 и 14 (рис. 7.113). Возможна работа и без внешних элементов. Если подключить внутреннее сопротивление микросхемы 2 кОм (выход 9) к выходу 14 и оставить неподключенными выводы 10 и 11, то получится время нахождения в нестабильном состоянии tQ = 30 не.

Микросхема FLK 101-74121 принадлежит к схемам ТТЛ-семейства. Она предназначена для напряжения питания 5 В и имеет параметры, типичные для схем этого семейства, которые приводятся в каталогах фирм-производителей.

Похожие статьи