Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Эмиттерно-связанная логика (ЭСЛ)

Схемы семейства эмиттерно-связанной логики создаются на базе

биполярных транзисторов. При создании этого семейства преследовалась

цель достижения максимально возможного быстродействия. Большое

быстродействие возможно только при переключении транзистора до того,

как он войдет в режим насыщения (см. Бойт/Шмуш, Электроника, ч. 3,

разд. 5.3).

Кажется, наиболее простым решением было бы построить схемы на базе

простых усилителей. В таких усилителях транзисторы никогда не заперты

полностью и никогда не проводят полностью. Переключение между

состояниями открыт—закрыт происходит чрезвычайно быстро. Однако у

усилителей на транзисторах много проблем с помехоустойчивостью. Разница

между уровнями L и Н мала, и состояние выхода нестабильно. Даже

изменение температуры может повлиять на выходной уровень, т. е. вызвать

самопроизвольные переходы с L на Н и наоборот.

В дифференциальном усилителе (см. Бойт/Шмуш, Электроника, ч. 3, разд.

3.7.2) возможно запереть один транзистор и управлять другим. Для

управляемого транзистора имеет место сильная обратная связь по току.

Вследствие этого малые изменения тока базы управляемого транзистора не

влияют на ток коллектора. Выходной уровень остается стабилен, хотя

управляемый транзистор не находится в насыщенном состоянии.

Рассмотрим схему на рис. 6.77. На ней изображена принципиальная схема

дифференциального усилителя. К базе транзистора Тг постоянно приложено

напряжение, например +2,7 В. Допустим, к базе Тх тоже приложено

напряжение +2,7 В. Оба транзистора открыты, и по эмиттерному

сопротивлению Re течет общий эмиттерный ток примерно 2 мА.

Если напряжение на базе Г, становится выше чем +2,7 В, то составляющая

тока эмиттера от Тх увеличивается. На RE увеличивается падение

напряжения, и транзистор Т2 должен закрыться.

Если к базе Тх приложено напряжение 3,7 В, то ток эмиттера равен

примерно 3 мА. Сопротивление R(i должно быть таким, чтобы напряжение

коллектора Тх не упало слишком сильно. Тх может проводить только до тех

пор, пока не приблизится к насыщению. Транзистор Т2 запирается, и ему

не нужен эмиттерный ток.

К выходу Z, запертого транзистора Т2 прикладывается +5 В. Это

напряжение высокого уровня. К выходу Zl запертого транзистора приложено

напряжение, полученное в результате падения напряжения на RE и

напряжения UCE проводящего транзистора. Оно равно примерно 3,5 В и

относится к нижнему уровню.

Если напряжение базы Г, немного падает или немного растет (например в

диапазоне ±0,1 В), то уровни Z, и Z, практически не меняются.

Они остаются стабильными. Если напряжение базы Тх падает ниже 2,7 В, то

происходит «опрокидывание». Транзистор Т2 начинает

проводить и вынуждает транзистор Т{ закрыться. Выход Zx становится

высоким уровнем, а выход Z2 — низким. Коллекторное сопротивление

Ra должно быть подобрано так, чтобы Т2 не входил в состояние насыщения.

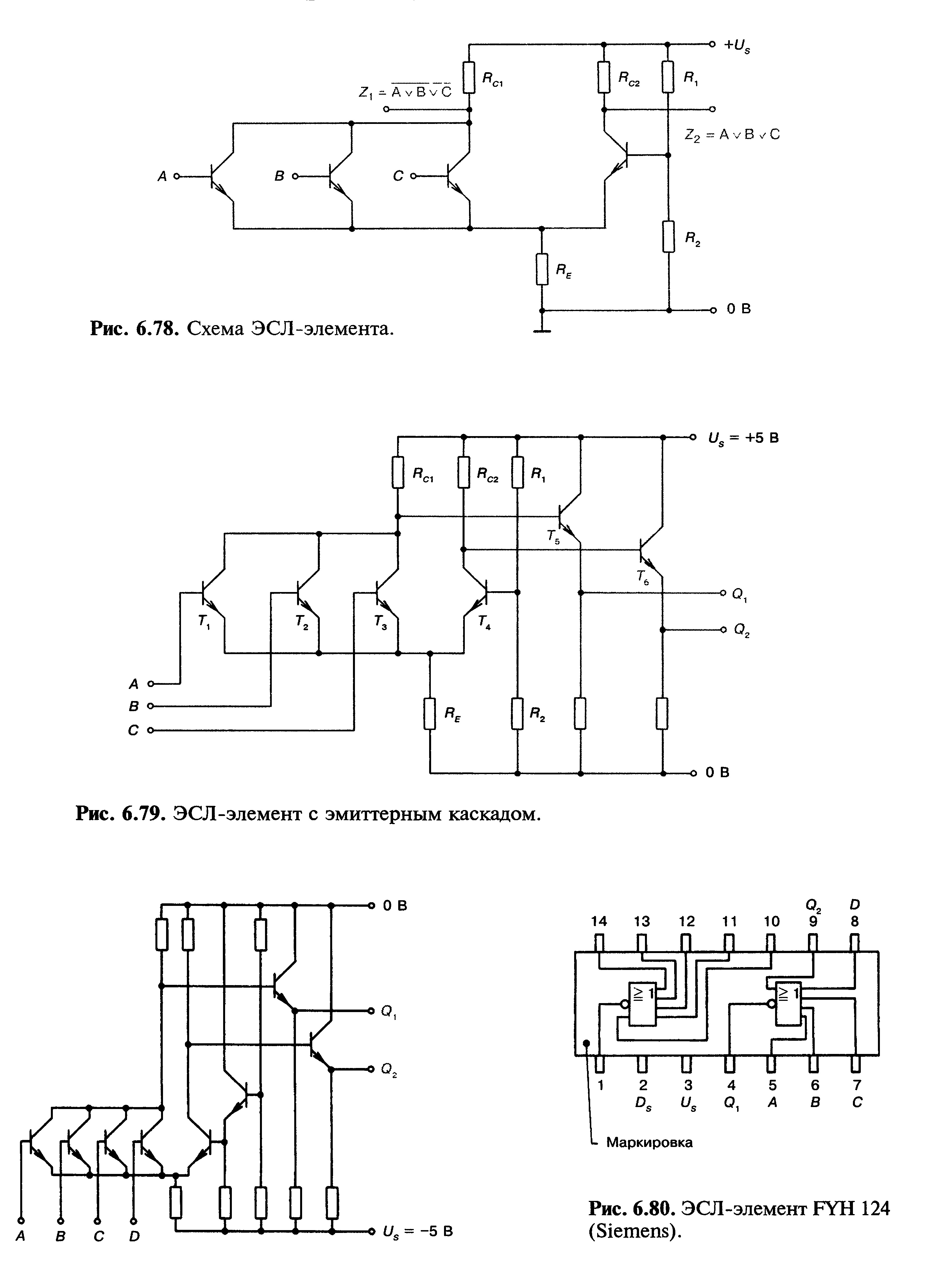

Параллельно с транзистором Тх можно включать другие транзисторы (рис.

6.78). Такое параллельное соединение является эквивалентом проводного

ИЛИ. При положительной логике на выходе Z, выполняется операция ИЛИ-HE.

Так как выход Z2 работает инверсно по отношению к Zv то на нем

выполняется операция ИЛИ.

Уровни Я и L выходов Zx и Z2 не годятся для управления последовательно

включенными логическими элементами. Поэтому к каждому из выходов

подключают эмиттерный повторитель. За счет этого происходит смещение

уровня и становится возможным управление большим количеством

последовательно включенных элементов.

Типовое значение коэффициента разветвления по выходу находится в

диапазоне от 20 до 30. На рис. 6.79 представлена принципиальная схема

элемента ЭСЛ с эмиттерными повторителями на выходах.

Фиксированное постоянное опорное напряжение для транзистора Т2 на схеме

(рис. 6.77) может быть получено с помощью делителя напряжения. В схеме

FYH 124 (рис. 6.80) используется дополнительный транзистор, который

обеспечивает стабильность опорного напряжения. Опорное напряжение

определяет так называемый порог переключения.

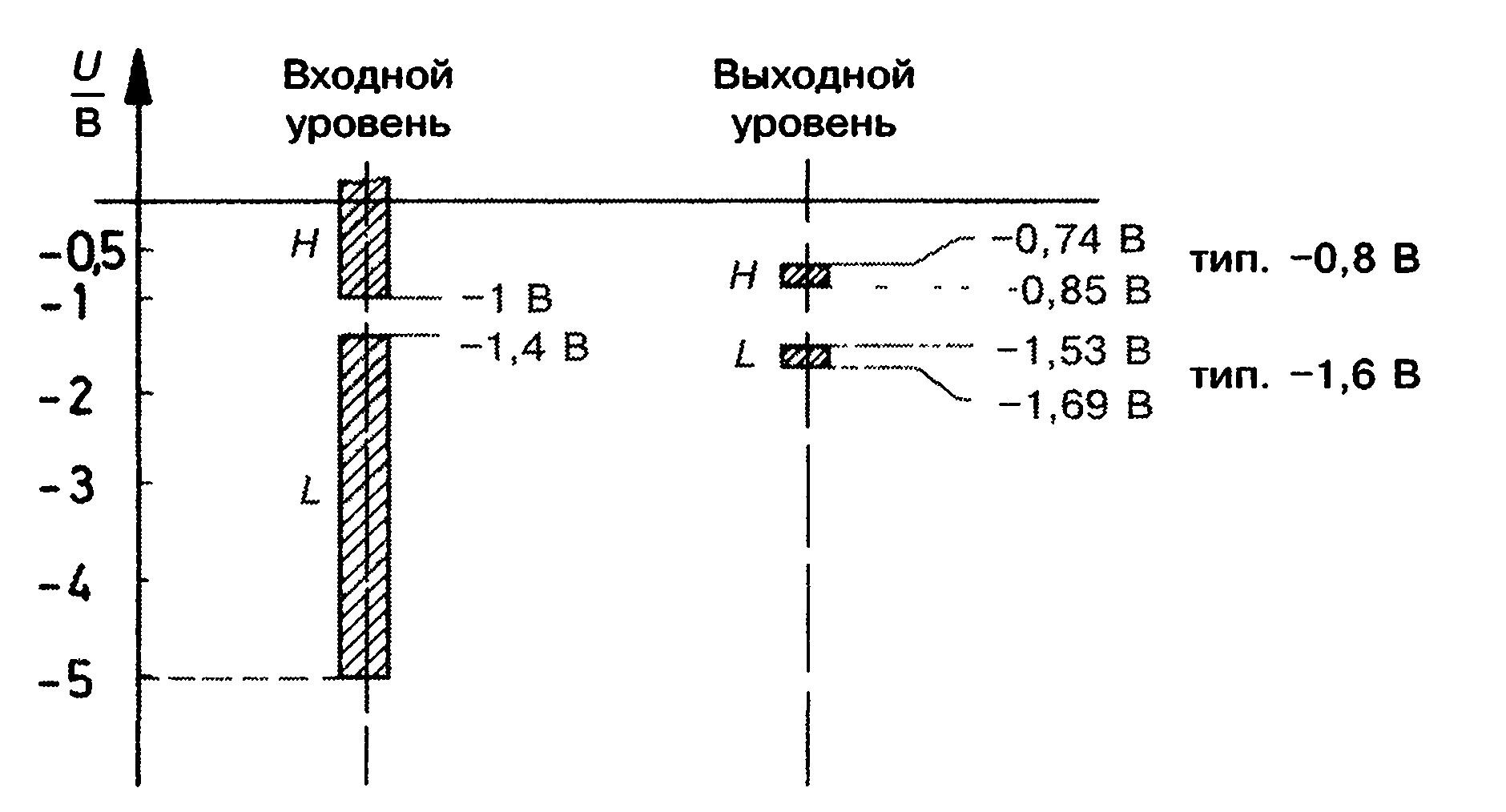

Изготовители ЭСЛ-схем используют чаще всего отрицательное напряжение

питания —5,0 В. Положительный полюс источника питания

заземляется. Для Н- и Z-уровней получаются отрицательные значения

напряжения. Диапазоны уровней схемы FYH 124 показаны на рис. 6.81.

Отрицательное напряжение питания улучшает помехоустойчивость. Разница

между напряжениями L- и //-уровней составляет всего около 0,4 В.

Помехоустойчивость вследствие этого мала. Изготовители указывают в

таблицах данных статическую помехоустойчивость 0,3 В. Вопрос

помехоустойчивости рассмотрен подробнее в разд. 6.4.5.

Особым преимуществом схем ЭСЛ является хорошее быстродействие. Среднее

время задержки tp составляет 2 не. Улучшенные технологии позволяют

уменьшить tp до 1 не. В настоящее время разрабатывается такое

супер-быстродействующее ЭСЛ-подсемейство.

Логические элементы подсемейства ЭСЛ являются самыми быстродействующими логическими элементами в настоящее время.

Рис. 6.81. Уровни напряжения ЭСЛ-элемента FYH 124

Очень высокие скорости переключения вызывают проблемы с

проводниками. При скорости 2 не мы заходим в верхнюю мегагерцевую

область (около 250 МГЦ). Провода активно излучают в высокочастотном

диапазоне, что приводит к взаимному влиянию рядом проложенных

проводников, то есть электромагнитная энергия излучается от одного

проводника к другому и наоборот. Время переключения логического

элемента сопоставимо с временем прохождения сигнала по проводнику.

Возникает проблема электромагнитной совместимости и в соединениях между

отдельными логическими элементами. При разводке схем следует также

учитывать волновые сопротивления проводников (дорожек на плате).

Схемы с ЭСЛ-элементами должны рассматриваться как высокочастотные

Необходимо применять экранирование. Если необходимо применять длинные

провода, то они должны быть коаксиальными. Целесообразно применять при

монтаже схемы высокоинтегральные микросхемы с высокой плотностью

элементов. Дорожки на платах между микросхемами должны быть как можно

короче.

В любом рабочем режиме в ЭСЛ-элементах всегда открыты много транзисторов, потребляющих соответствующие токи.

Элементы ЭСЛ-подсемейства отличаются высоким энергопотреблением.

Каждый элемент потребляет примерно 60 мВт. Это в шесть раз больше, чем

у стандартных ТТЛ-элементов. В следующей таблице приведены важнейшие

параметры ЭСЛ-элементов:

схемы.

Схемы подсемейства ЭСЛ

Напряжение питания Энергопотребление (на вентиль) Быстродействие Макс. частота переключения Типичный зазор между уровнями

-5 В 60 мВт 0,5 не 1 ГГц 0,3 В

ЭСЛ-элементы применяются в таких схемах, где высокая рабочая скорость

имеет абсолютный приоритет. Наряду с немногими прикладными областями

промышленных систем управления это прежде всего военные технологии.

Похожие статьи