Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

ЯБ-триггеры с доминирующим Я-входом

Наличие запрещенных комбинаций для тактируемых &У-триггеров вызвало идею построения триггера, который принудительно устанавливает Qx в 0 при S= 1 и R = 1, при подаче синхроимпульса. Это становится возможным благодаря особенному подключению входов.

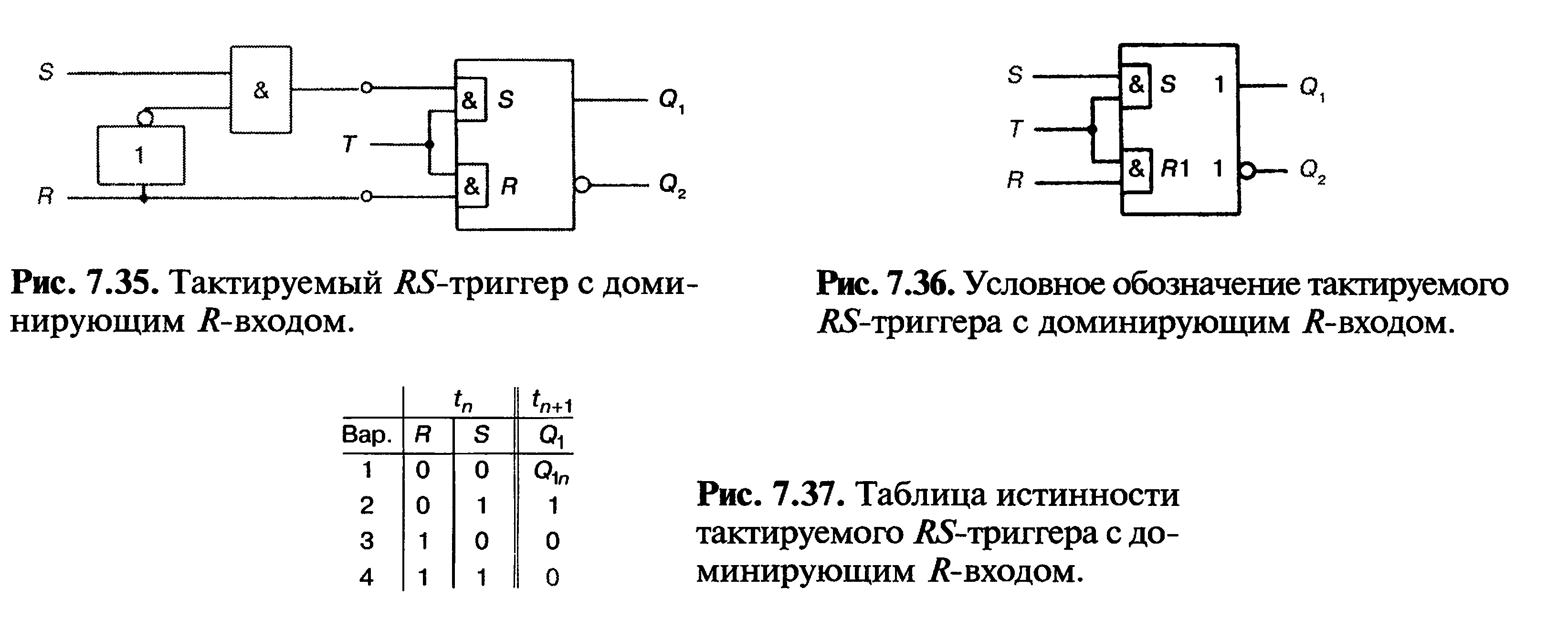

На рис. 7.35 показано такое соединение входов. При S = 1 и R = 1, 1-сигнал не может воздействовать на триггер, так как на выходе элемента НЕ действует 0. И-элемент запирается. 1-сигнал на R разрешает сброс. Режим установки при S = 1 и R = 0 остается возможен, так как теперь на выходе элемента НЕ действует 1 и И-элемент имеет на выходе 1.

Такой триггер называется .RS'-триггером с доминирующим /?-входом, или ^триггером. Правило его работы следует из условного обозначения на рис. 7.36 (см. также разд. 7.1). Оно гласит: если оба входа триггера S, R и вход Т имеют уровень 1, то при сигнале синхронизации 1 Q{ устанавливается на 0, a Q2 — на 1.

Таблица истинности тактируемого ЛУ-триггера с доминирующим R-входом представлена на рис. 7.37. Разумеется, существует также тактируемый RS-триггер с доминирующим ^-входом (см. контрольный тест).

Похожие статьи