Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Требуемая функция и реальная функция

Под требуемой функцией понимают логическую функцию, которую должна

реализовывать схема на основе своей структуры. Реальной функцией

является функция, которую на самом деле реализует схема в результате

своей работы.

При безупречно функционирующей схеме требуемая функция и реальная функция должны совпадать.

Если требуемая функция и реальная функция неодинаковы, то схема

содержит одну или несколько ошибок, которые должны быть найдены и

устранены.

Как определить реальную логическую функцию

Требуемая логическая функция определяется из заданной для схемы таблицы

истинности. Реальная логическая функция определяется путем тестовых

измерений.

Перед началом измерений нужно установить соответствие уровней напряжения логическим состояниям 0 и 1.

Для определения логического состояния, или уровня напряжения, что

является одним и тем же, требуется так называемый логический тестер. Он

представляет собой маленький транзисторный усилитель и один или два

диода для индикации показаний.

Прибор с одним индикаторным диодом показывает только логический уровень

1, или ВЫСОКИЙ уровень (для данного примера +5 В). Если диод не

светится, значит, логический уровень равен 0. Такой прибор не позволяет

обнаружить обрыв провода с логическим состоянием 0. Состояние 0 в

большинстве случаев соответствует цифровой земле, а не неподключенному

проводнику.

Лучше применять приборы с двумя светодиодами. Красный диод показывает,

например, логическое состояние 1, а зеленый — логическое

состояние 0. Если не горит ни один диод, значит в линии обрыв. Такой

логический тестер на маленьком транзисторе можно собрать самому. Вход

должен быть как можно более высокоомным.

Наряду с малыми логическими тестерами в продаже имеются более сложные

приборы, позволяющие одновременно испытывать все входы и выходы.

Вследствие этого значительно уменьшается время тестирования схемы.

Последним звеном эволюции тестеров стали компьютеризированные тестовые

стенды, которые автоматически тестируют всю схему и указывают дефекты.

Покажем на примере, как определяется реальная логическая функция.

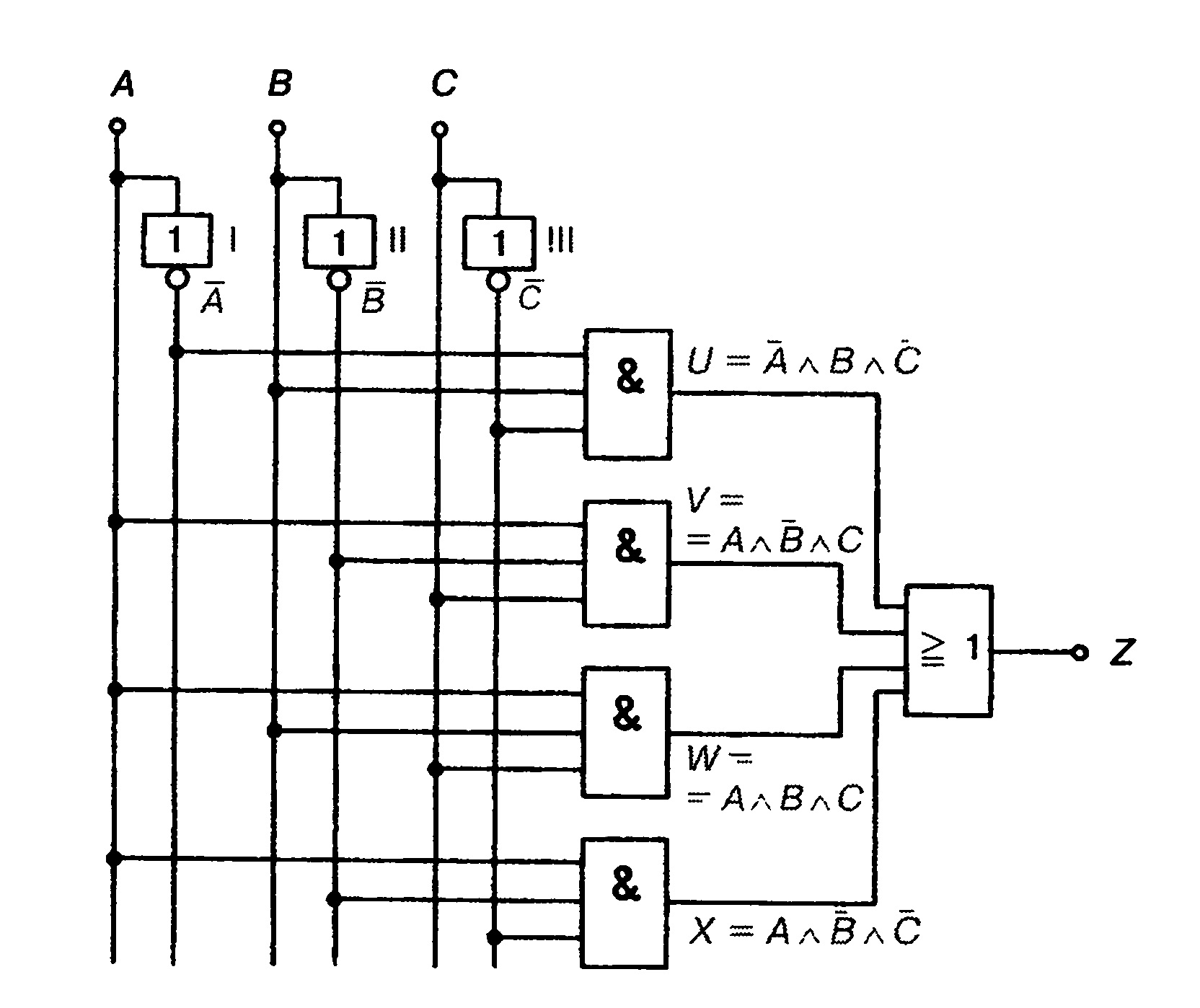

Предположим, что имеется в наличии схема, изображенная на рис. 3.10. И

у нас есть простой логический тестер, определяющий состояния 1 и 0 или

соответственно ВЫСОКИЙ и НИЗКИЙ уровни.

Рис 3.10. Цифровая схема

Присвоим логическим состояниям уровни напряжения:

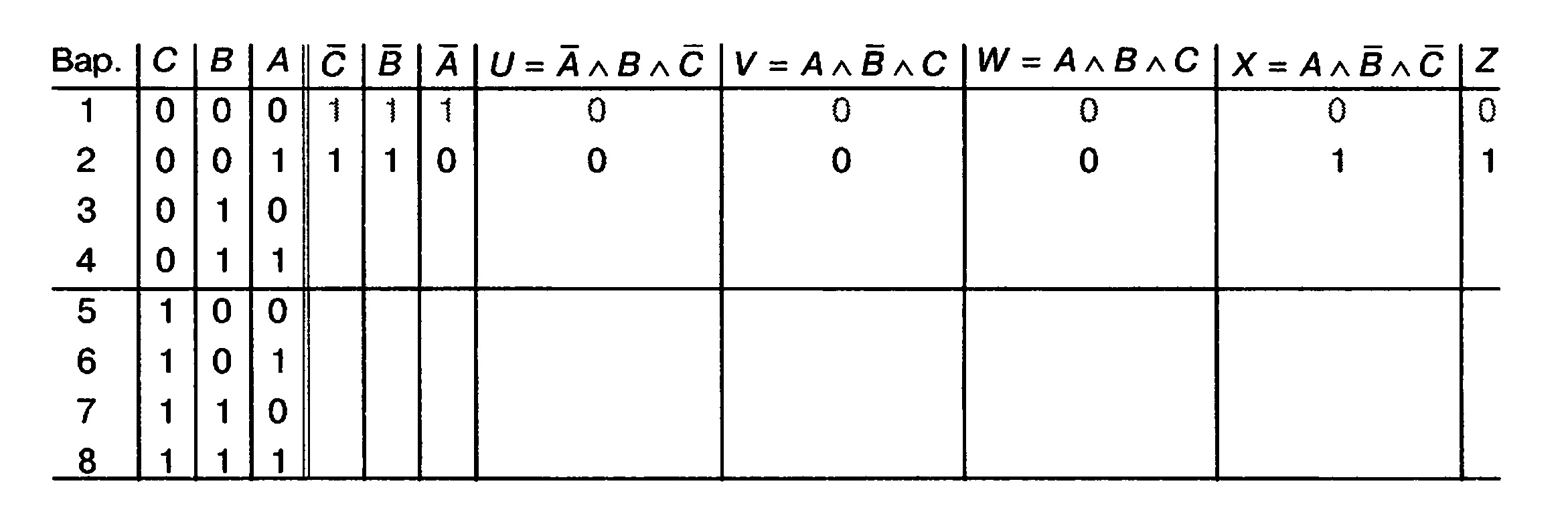

Протокол измерений представим в виде таблицы (рис. 3.11).

Рис 3.10. Таблица истинности

Сначала измеряется вариант 1. Все три входа заземляются и получают состояние 0.

Затем тестируются выходы отдельных элементов — С, В, A, U, V, W,

X, Z — и заносятся в таблицу (обозначено серым на рис. 3.11).

Рис. 3.11. Таблица истинности.

После первого варианта измеряется вариант 2. На вход А подается 1, В и С остаются 0.

Снова измеряются выходы отдельных элементов, и их состояния заносятся в таблицу.

Это измерение производится для всех 8 возможных вариантов.

Полученная таблица отражает реальную логическую функцию, реализуемую схемой.

Если предполагается, что схема исправна, то можно ограничиться

определением состояния выхода Z. Если состояние Z отличается от

требуемого, то проводится тест всех элементов.

Поиск дефекта схемы

Имея заданную таблицу истинности и таблицу протокола измерений, можно по их расхождению определить ошибку в схеме.

Определение ошибки происходит путем сравнения требуемой логической функции и реальной.

Если требуемая логическая функция и реальная совпадают, то схема не

содержит ошибок. Сначала сравнивают состояния выходов всей схемы. Если

они совпадают, дальнейшее сравнение не требуется. Схема в порядке. Если

состояния выходов различаются, то проводится пошаговый тест всех

элементов, начиная от входных.

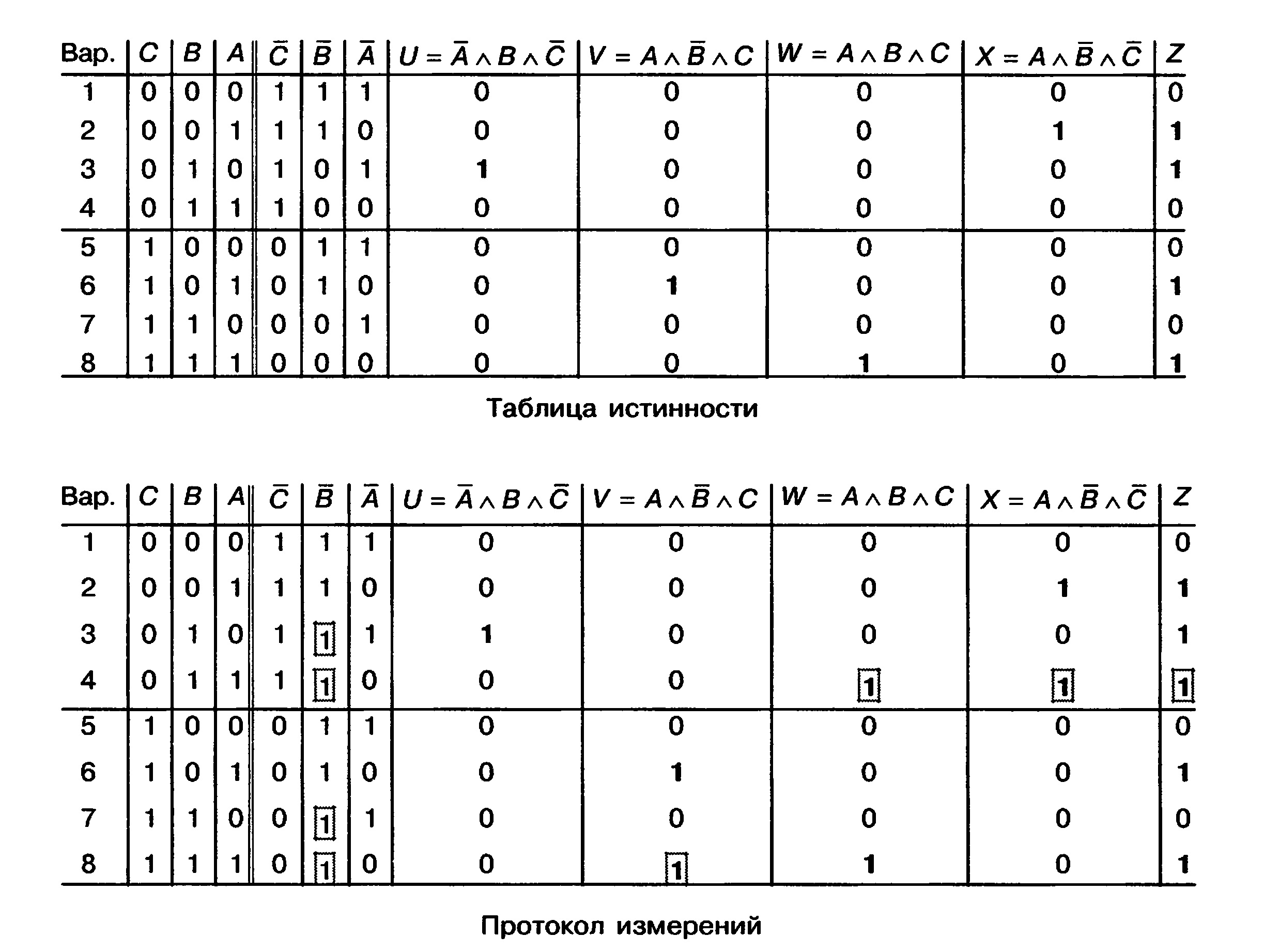

На рис. 3.12 изображена таблица истинности схемы по рис. 3.10 и таблица измерений.

Какие логические элементы работают неправильно?

Если проверять столбцы слева направо, то при В обнаруживается ошибка.

Это элемент НЕ, который должен инвертировать состояние входа В (элемент

II), всегда имеет логическое состояние 1. Итак, он не работает.

Ошибка элемента //действует на выход VиХ, так как только эти элементы

используют сигнал В. Для Vи Алогические операции выполнены верно

при условии, что В всегда равен 1. Элементы Vи X, следовательно, исправны.

Следующая ошибка обнаруживается на элементе W Следовательно, элемент

Wнеисправен. Ошибку при выполнении логической операции нельзя списать

на счет элемента II, так как W = А л В л С не включает в себя В.

В результате проверки выяснилось, что замене подлежат логические элементы II и W.

Рис. 3.12. Таблица истинности и протокол измерений цифровой схемы

Контрольный тест

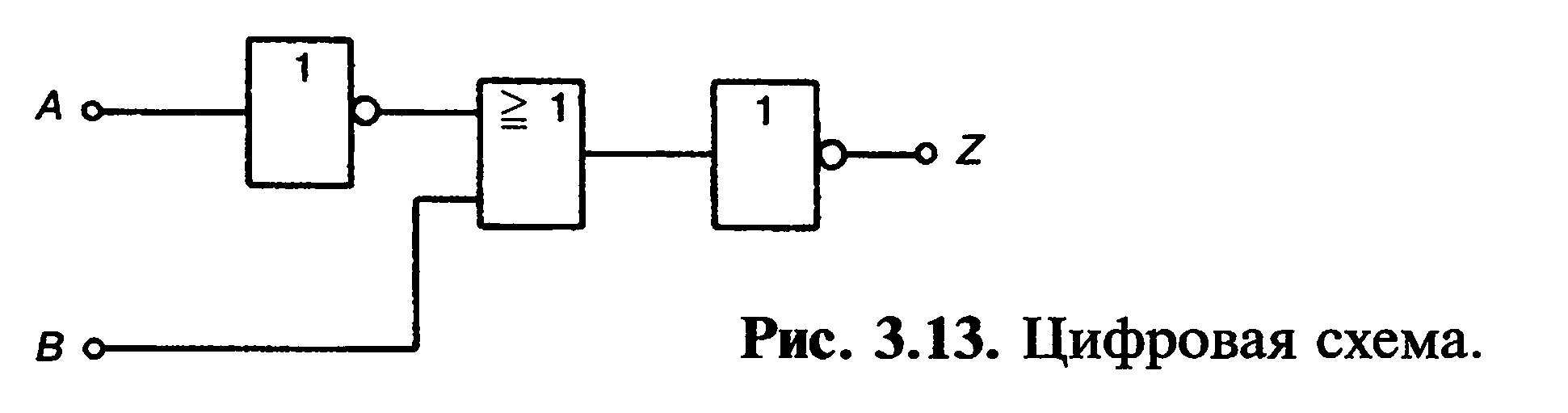

1. Составьте таблицу истинности для схемы на рис. 3.13.

2. Составьте таблицу истинности для схемы рис. 3.14.

3. В схеме на рис. 3.14 элемент //дефектен. На его выходе детектируется

всегда логическое состояние 1. Какую логическую функцию выполняет схема

вследствие этого дефекта? Изобразите реальную функцию схемы в виде

таблицы истинности.

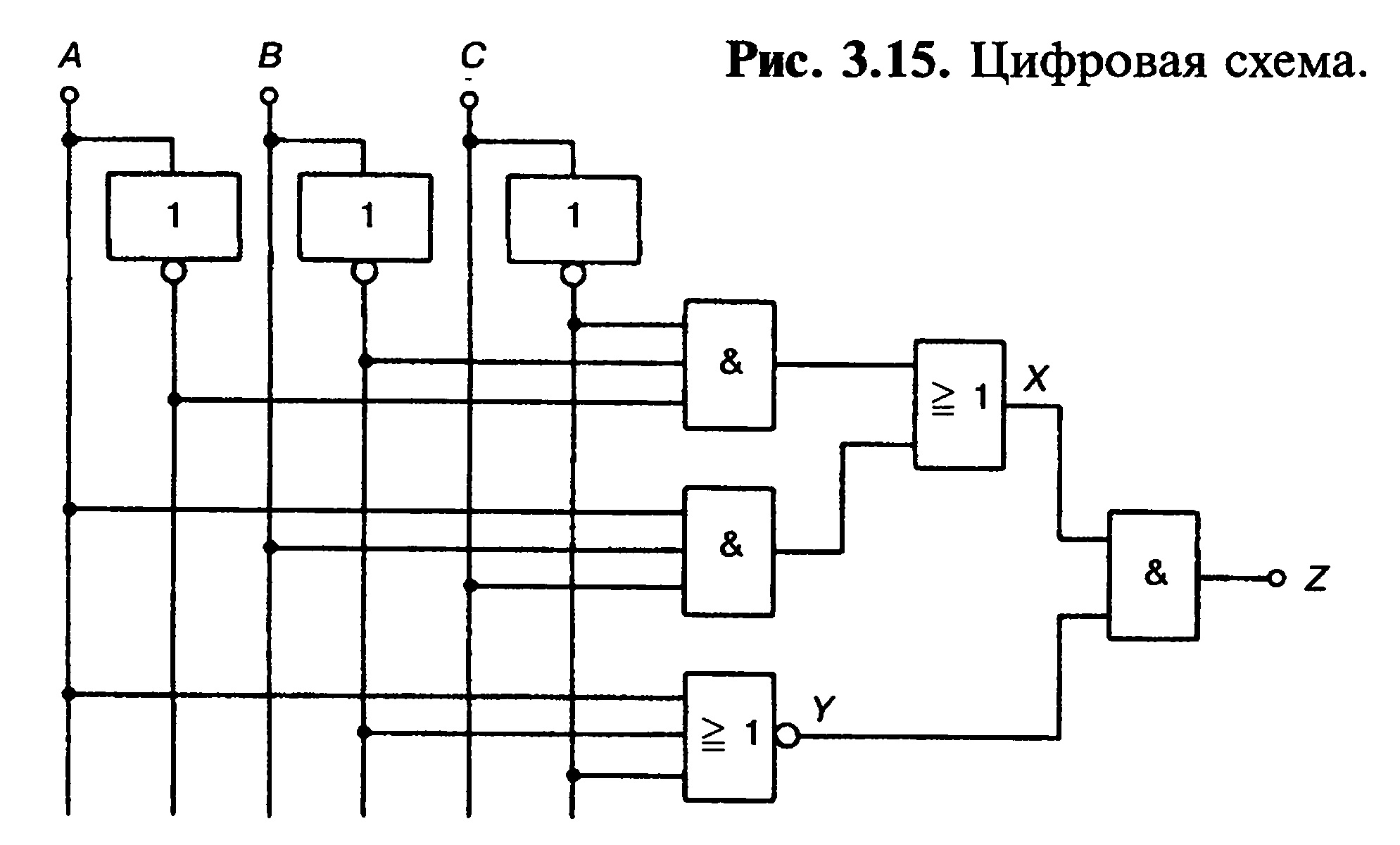

4. Определите для схемы на рис. 3.15 логическую функцию и изобразите таблицу истинности.

5. Постройте схему, отвечающую следующей логической функции:

6. Постройте схему и таблицу истинности, отвечающую следующей логической функции:

Z = AvBvCaAvBaCaDvAaD.

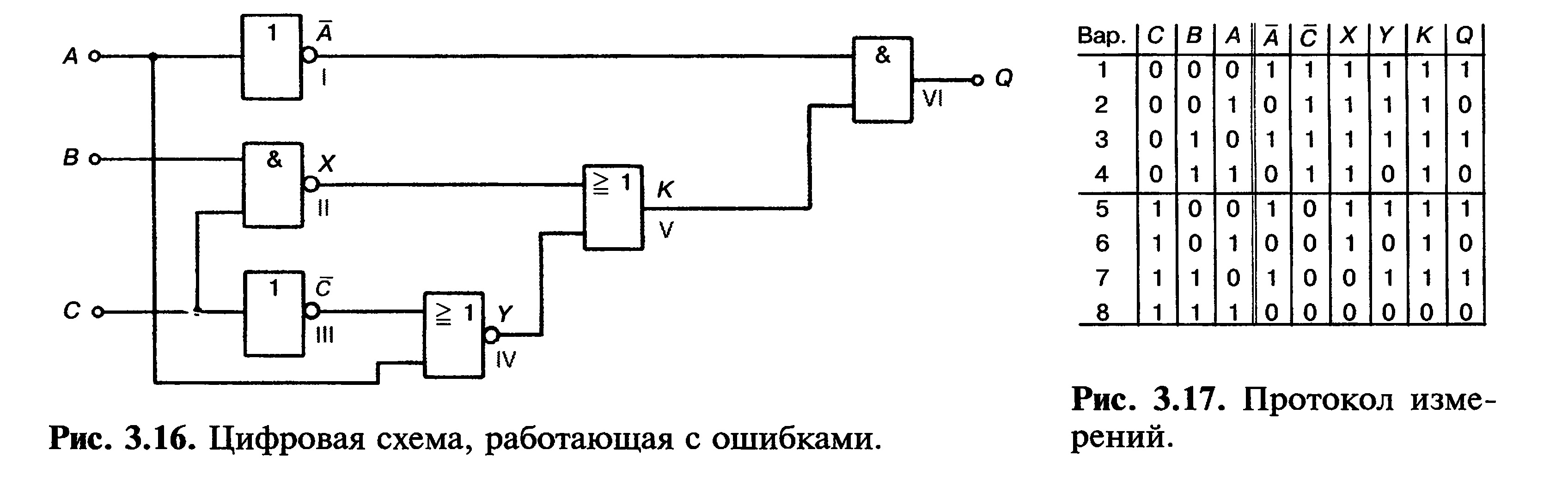

7. Схема на рис. 3.16 работает с ошибками. Таблица результатов

тестирования (протокол измерений) изображена на рис. 3.17. Определите

дефектные логические элементы.

Похожие статьи