Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Логические элементы на МОП-транзисторах

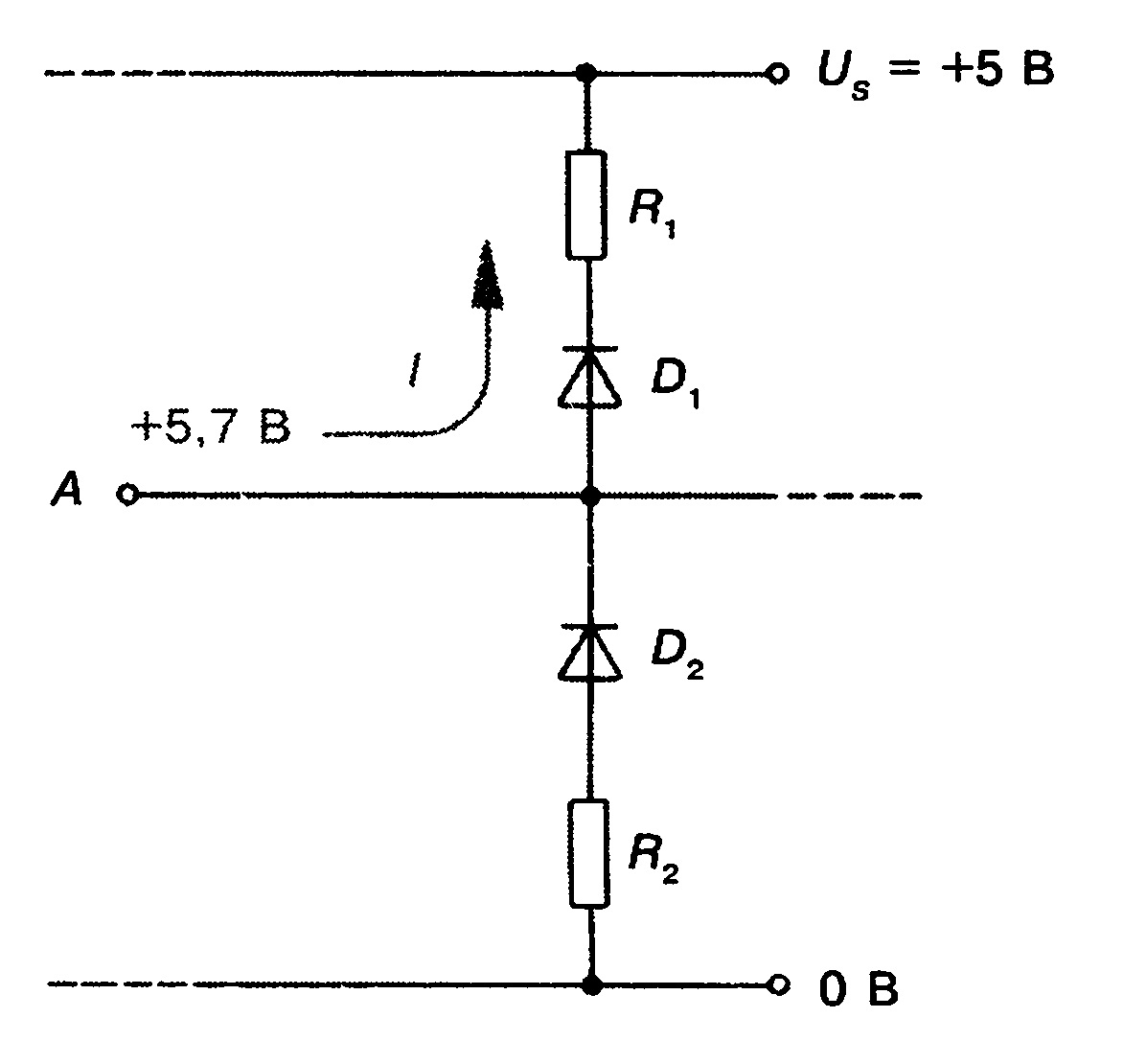

Входы современных КМОП-микросхем защищены от воздействия статических разрядов. В качестве защиты используют диодные схемы согласно рис. 6.107. Если напряжение входа превышает напряжение питания на величину примерно 0,7 В (напряжение открытия диода), диод Dx откроется и лишний ток уйдет к источнику питания. В схеме на рис. 6.107 это происходит при входных напряжениях выше +5,7 В. При отрицательных входных напряжениях, начиная с —0,7 В, открывается диод Dr

Концентрация основных носителей заряда в полупроводниковых зонах

диодов очень мала, поэтому они обладают большим динамическим

сопротивлением.

Вследствие этого очень высокое входное сопротивление КМОП-элементов

только незначительно уменьшается при добавлении диодов. Кроме того,

малое динамическое сопротивление диодов при ошибочной полярности

питания привело бы к их мгновенному выходу схемы из строя, так как

через D, и D2 потек бы ток короткого замыкания.

Если на вход элемента подается большой статический заряд, то

соответствующий полевой транзистор может выйти из строя, несмотря на

диодную защиту. Из-за больших динамических сопротивлений заряд может не

успеть достаточно быстро рассосаться, так что может возникнуть опасное

высокое напряжение. При работе с МОП-схемами следует принимать обычные

меры предосторожности против статического электричества.

КМОП-схемы имеют широкую область применения. Они достаточно быстры для

решения многих технических задач и отличаются малым энергопотреблением.

Даже микросхемы высокой степени интеграции очень выгодны при

производстве в больших количествах.

Контрольный тест

1. Что понимают под схемами одного семейства?

2. Назовите основные семейства логических схем.

3. Что такое бинарные уровни напряжения?

4. Что понимают под положительной логикой, под отрицательной?

5. Чем отличается рабочая таблица от таблицы истинности?

6. Составьте для схемы на рис. 6.108 рабочую таблицу.

7. Какую логическую операцию производит схема на рис. 6.108 при положительной и при отрицательной логике?

8. На рис. 6.109 показаны два диапазона уровня. Какой является Н-диапазоном и какой L-диапазоном?

Рис. 6.107. Защитная схема против статического разряда

9.

Что понимают под передаточной характеристикой? Нарисуйте примерную

передаточную характеристику.

10. Разъясните понятия «быстродействие» и «время нарастания сигнала».

11. Что такое входной нагрузочный коэффициент?

12. В таблице данных на элемент указано: коэффициент разветвления Fq = 10. Что это значит?

13. Как устроены ДТЛ-элементы?

14. Нарисуйте схему типового ТТЛ-элемента с тремя входами и двухтактным выходом.

15. Какую операцию производит схема на рис. 6.110 при положительной логике?

16. Часто можно услышать понятия «насыщенный элемент» и

«ненасыщенный элемент». Что значат эти понятия?

17. Какие преимущества и недостатки имеет подсемейство ТТЛ-схем с

пониженным энергопотреблением по отношению к стандартным ТТЛ-эле-ментам?

18. Как устроены яМОП-элементы?

19. Упорядочите известные Вам семейства логических элементов

а) по энергопотреблению,

б) по быстродействию.

20. Нарисуйте схему КМОП-элемента с двумя входами, которая производит

при положительной логике операцию ИЛИ-НЕ, и объясните принцип действия

этой схемы.

Похожие статьи