Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

ТТЛ-схемы

Строение и принцип действия ТТЛ-элементов

Сокращение ТТЛ обозначает транзисторно-транзисторная логика. Логические

элементы схем этого семейства строятся исключительно на биполярных

транзисторах. Только для сдвига уровня и отвода напряжения применяются

диоды. Сопротивления служат в качестве делителей напряжения и

ограничителей тока.

TTL-элементы производятся исключительно в виде интегральных микро-

К базе приложено напряжение чуть

ВЫШе 0,7 В относительно земли. При за- мыкании эмиттера на землю начинает

течь базовый ток. Величина базового тока определяется значением базового сопротивления и напряжения питания Us (рис. 6.40).

Величина базового тока выбирается такой, чтобы мультиэмиттерный транзистор надежно управлялся в режиме насыщения.

схем.

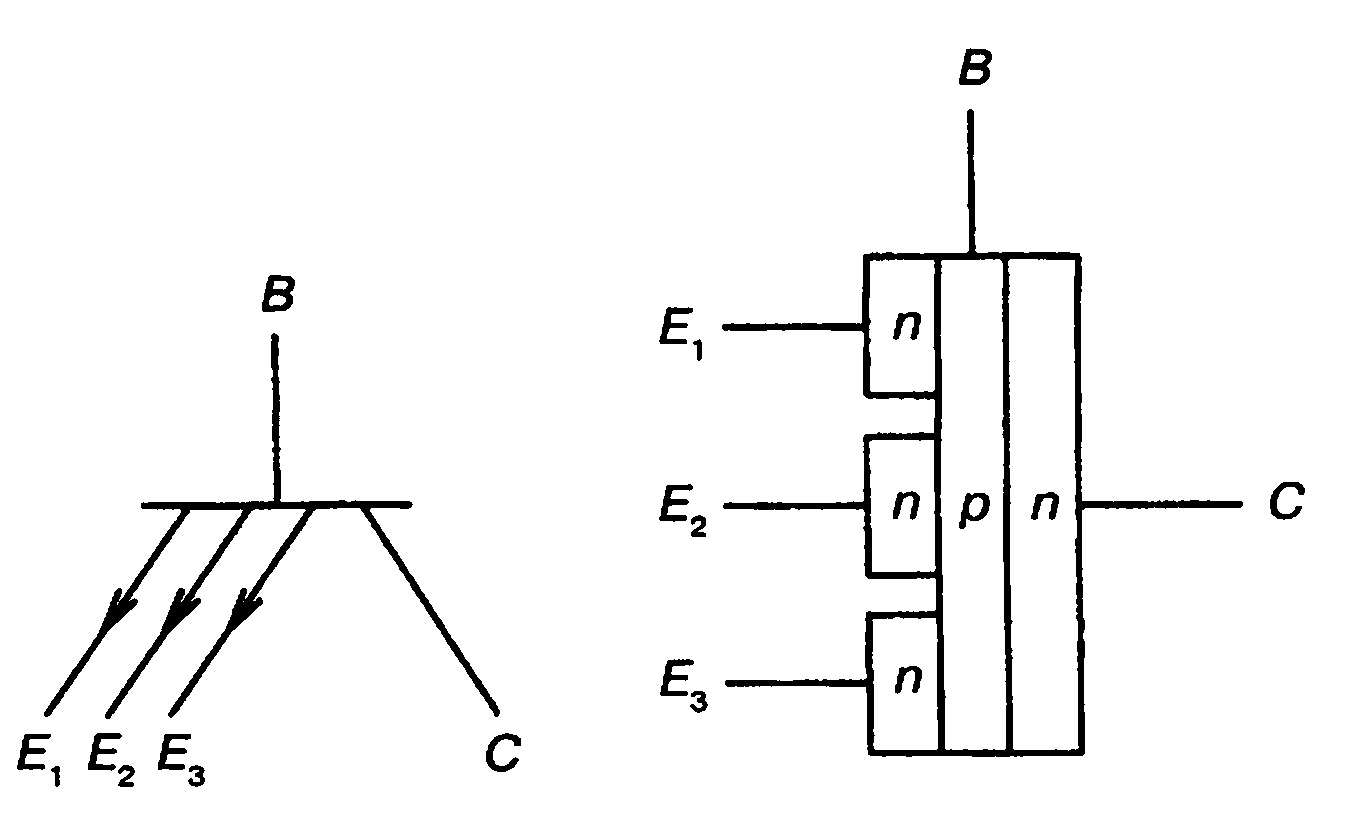

Рис. 6.39. Мультиэмптерный транзистор

Новым элементом является так называемый мультиэмиттерный транзистор.

Структура такого транзистора показана на рис. 6.39. С общей базой

граничат три эмиттерных зоны. Таким образом, образуются три разделенных

PN-перехода между базой и эмиттерами. Эти PN-ne-реходы можно

рассматривать как диоды.

Режим насыщения является высоко-вероятностным режимом. Напряжение

коллектор-эмиттер UCE падает при этом до значения насыщения UCEsat. Оно

равно примерно 0,2 В.

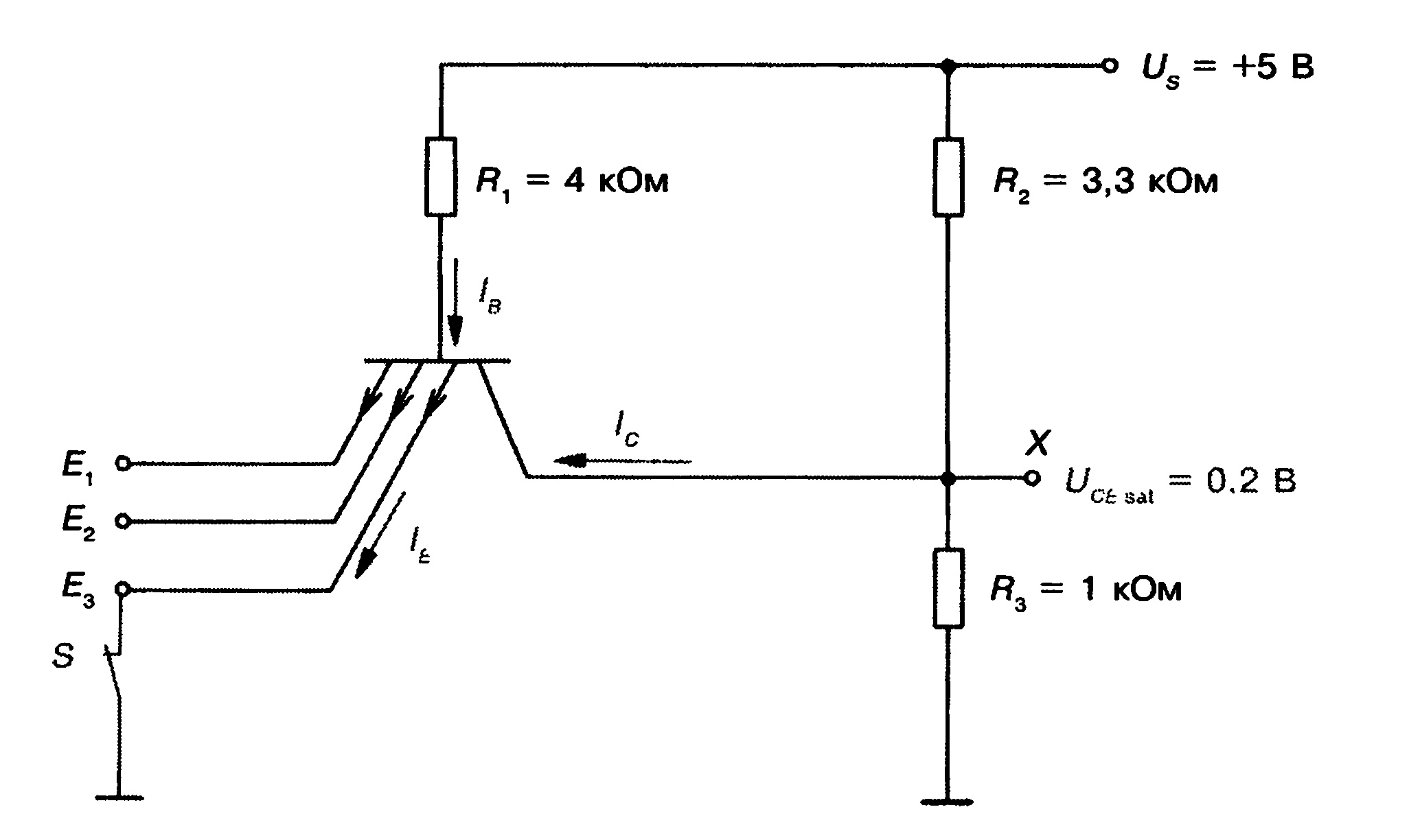

Рис. 6.40. Схема на мультиэмиттерном транзисторе

Сопротивление на рис. 6.40 должно быть равно примерно 3,3 кОм. Ток

/с будет тогда небольшим. Ток эмиттера 1Е равен приблизительно току 1В.

Обычно токи эмиттеров выбираются между 1 мА и 1,6 мА.

Если два или все три эмиттера в схеме на рис. 6.40 заземлены, то

напряжение в точке X практически не меняется. X остается на уровне

примерно 0,2 В. Что изменится, если эмиттер Е3 заземлить, а на эмиттеры

Ех и Е2 подать напряжение питания +5 В? PN-переходы между эмиттерами

EVE2 и базой будут закрыты (плюс на «-зоне). PN-переход Еъ к базе

остается открытым. Транзистор продолжает оставаться в состоянии

насыщения. Напряжение в точке X не меняется.

Если уровню L поставить в соответствие напряжение от 0 В до 0,4 В, то

при приложении хотя бы к одному из эмиттеров схемы на рис. 6.40 уровня

L на выходе X будет также действовать низкий уровень L.

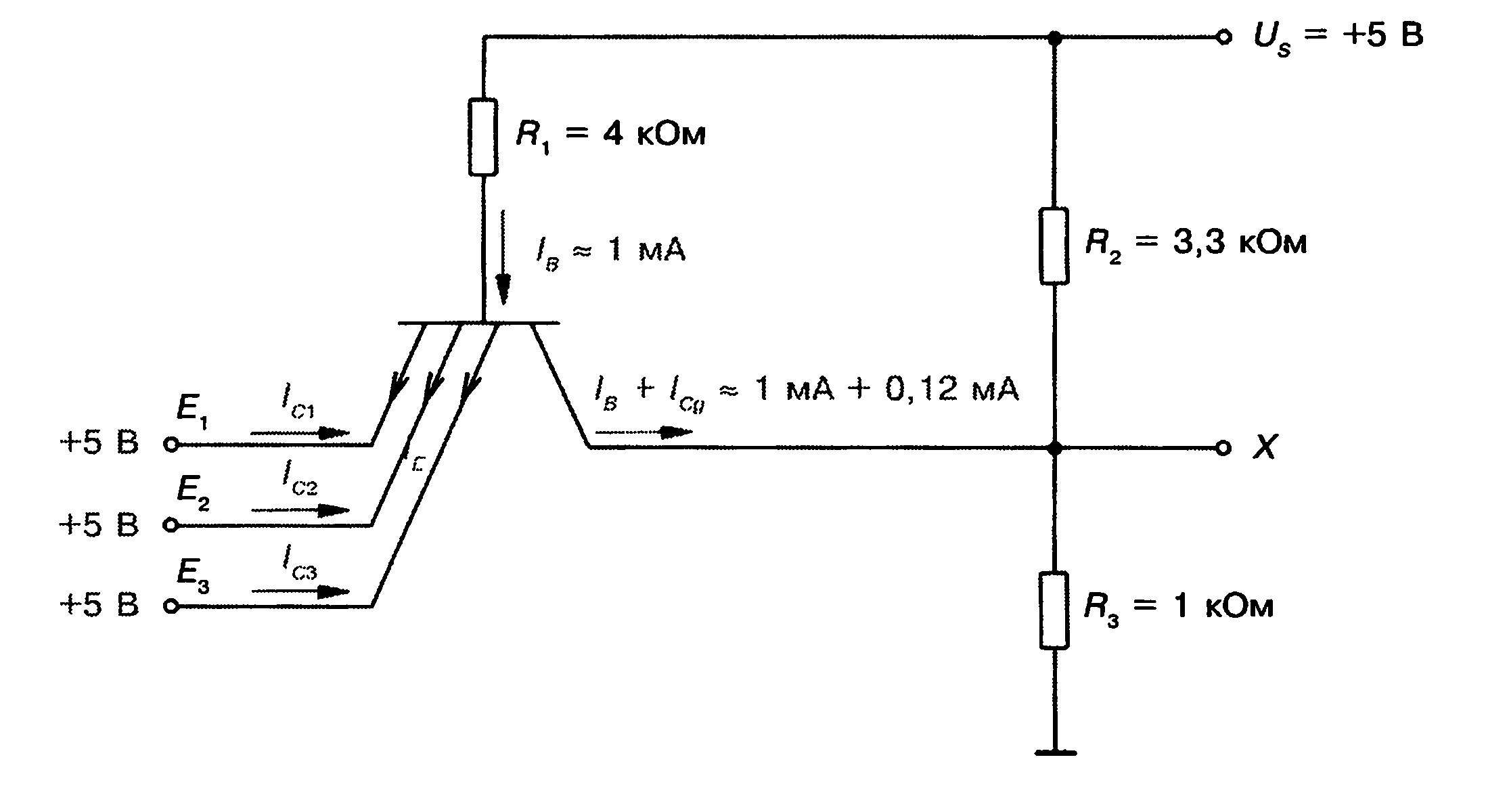

Совершенно иначе работает схема (рис. 6.41), если на все эмиттеры

подать напряжение питания (ВЫСОКИЙ уровень Н). К эмиттерным зонам

приложен потенциал +5 В. В точке X благодаря делителю напряжения R2/R3

будет напряжение примерно 0,45 В, то есть напряжение, которое

соответствует уровню L.

К коллектору приложено напряжение примерно 0,45 В, к эмиттеру —

+5 В. Теперь мультиэмиттерный транзистор работает в инверсном режиме,

т. е. эмиттер и коллектор обменялись функциями. Эмиттеры работают как

коллекторы, коллектор работает как эмиттер.

Рис. 6.41. Схема на мульти эмиттерном транзисторе в инверсном режиме

Если ко всем эмиттерам приложен высокий Н-уровень, то мультиэмиттерный транзистор работает в инверсном режиме.

Базовый ток течет от источника питания через Rx и на землю (см. рис.

6.41). Типичное значение базового тока равно 1 мА. Однако токи

коллектора /а, 1а и 1а от эмиттерных входов Ev Ег и Еъ относительно

малы. Каждый ток коллектора не превышает 40 мкА. Благодаря специальной

технологии добились, что так называемое инверсное усиление тока

мульти-эмиттерного транзистора очень мало. Следовательно, управляемые

элементы потребляют относительно небольшой ток.

Инверсное усиление по току мультиэмиттерного транзистора много меньше единицы.

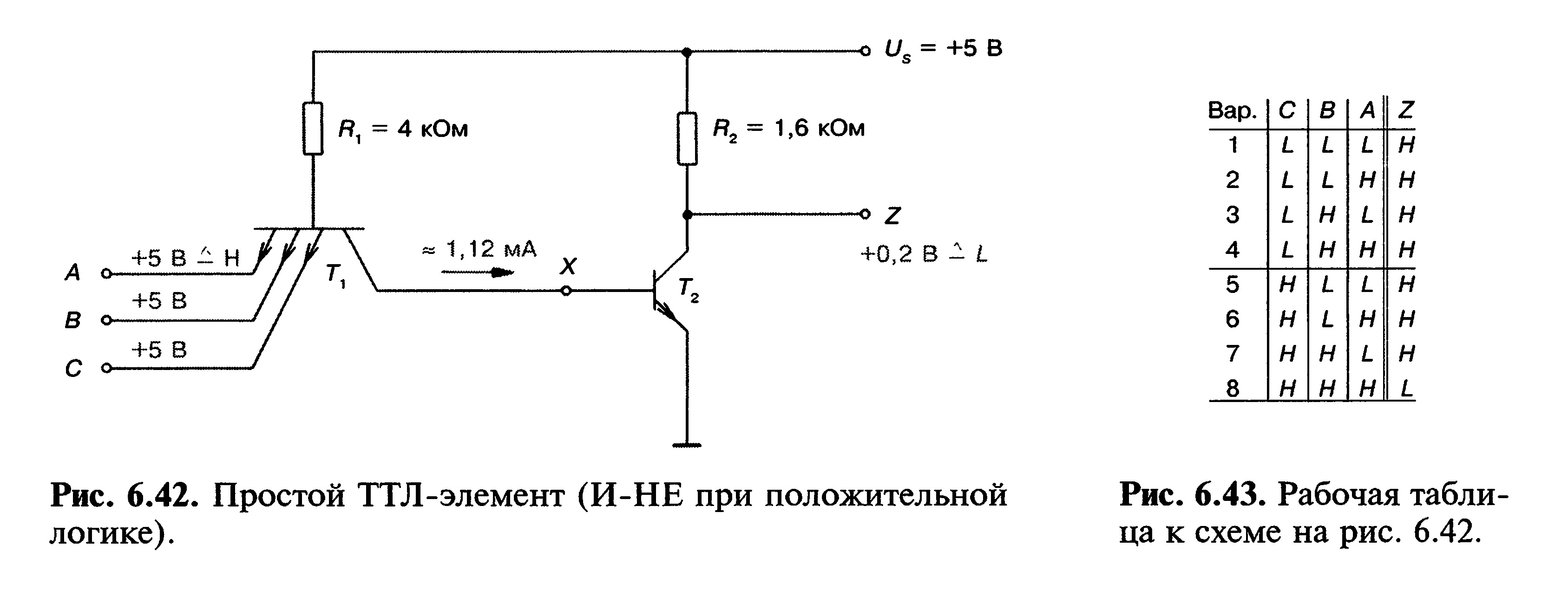

На выходе Xпредставленной на рис. 6.41 схемы напряжение поднимется с 1

до примерно 2 В. Этого напряжения недостаточно для достижения высокого

уровня Н. Оно слишком низкое. Однако этим напряжением можно управлять

последующим транзистором, как показано на рис. 6.42. Сопротивления

делителя напряжения R2 и R3 можно тогда не использовать. Функцию

резистора R} берет на себя участок база-эмиттер Т2. Высокоомное

сопротивление R2 заменяется Rc и участком база-коллектор транзистора

Т2. Схема имеет входы А, В, Си выход Z.

Если на входах А, В и С действует уровень Н, то Г, работает в инверсном

режиме. Транзистор Т2 войдет в режим насыщения. На выходе Z будет

напряжение примерно 0,2 В. Такое напряжение относится к уровню L.

Если по меньшей мере на одном из входов действует уровень L, то

мультиэмиттерный транзистор Г, работает нормально в режиме насыщения.

Напряжение на его коллекторе падает примерно на 0,2 В. Т2 запирается.

На выходе Z действует уровень Н. Рабочая таблица схемы рис. 6.42

представлена на рис. 6.43. При положительной логике получается

логический элемент И-НЕ.

Как будет работать схема при открытом входе? Под открытым входом

понимают вход, который не подключен ни к уровню L, ни к уровню Н. То

есть ко входу ничего не подключено, и он висит в воздухе. Такой вход не

в состоянии понизить напряжение в точке X схемы на рис. 6.42 до 0,2 В.

То есть он не может заставить мультиэмиттерный транзистор проводить ток.

Если на двух входах схемы рис. 6.42 действует уровень Н, а третий вход

открыт, то мультиэмиттерный транзистор будет работать в инверсном

режиме — так же, как если бы на все три входа действовал

//-уровень.

Для ТТЛ-схем открытый вход приравнивается ко входу с высоким Я-уровнем.

Посмотрим внимательнее на схему (рис. 6.42). Заметно, что

мультиэмиттерный транзистор никогда не заперт. Он всегда проводит

— либо в прямом, либо в инверсном режиме. Базовый ток есть

всегда. В прямом режиме он течет к входам, которые лежат на уровне Z. В

инверсном он течет к базе транзистора Тг Значит, носители зарядов

базовой зоны при переключении режимов не должны рассасываться, и

переключение из одного состояния в другое происходит очень быстро.

Мультиэмиттерный транзистор очень быстро переключается из прямого

режима в инверсный и наоборот, так как носителям зарядов в базе при

переключении не нужно рассасываться.

Время переключения для транзистора Т2 получается также малым. Носители

заряда базы Т2 как раз успевают рассосаться за время перехода

мультиэмиттерного транзистора Тх из состояния насыщения в запертое

состояние.

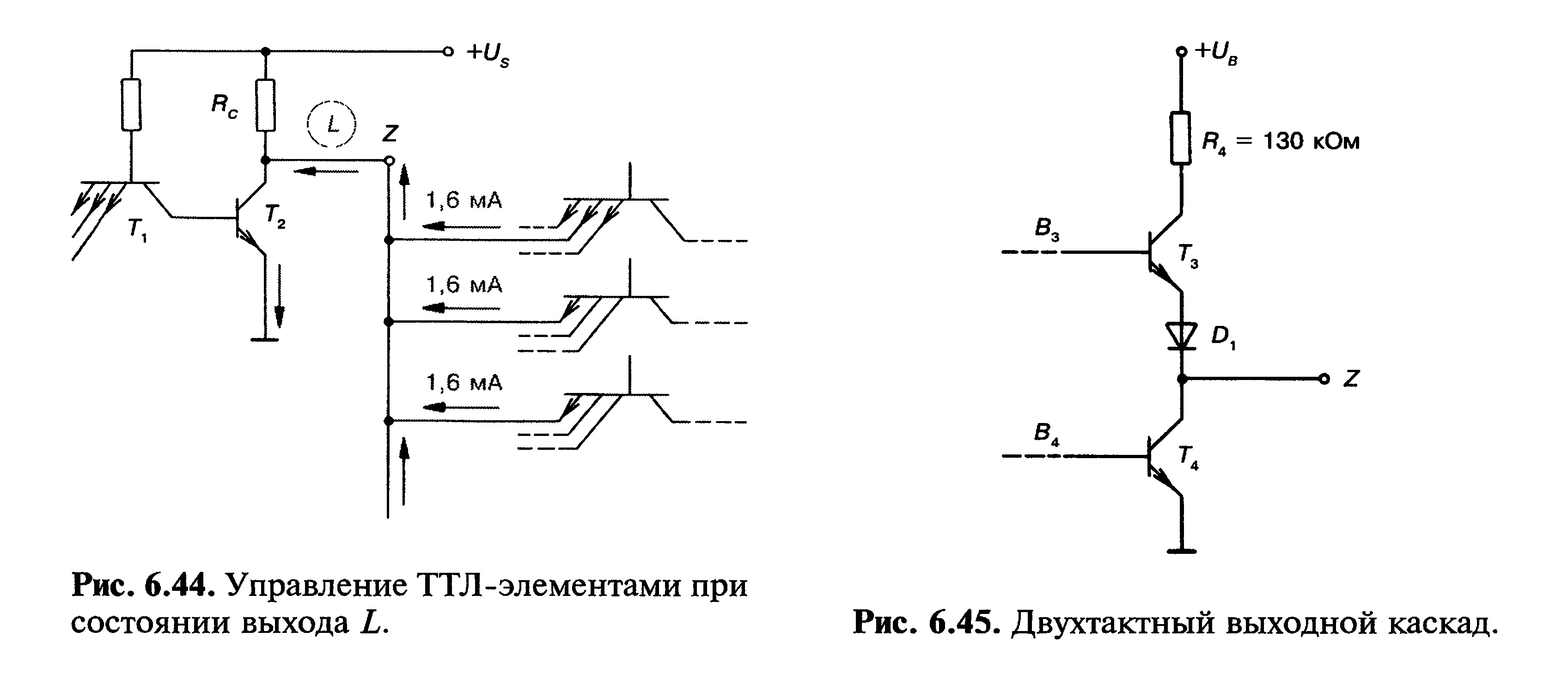

Представленная на рис. 6.42 ТТЛ-схема не очень хорошо подходит для

управления последовательно подключенными ТТЛ-элементами. Выход Z в

состоянии L должен принимать от каждого присоединенного входа ток

примерно 1,6 мА (рис. 6.44). При десяти присоединенных входах

(коэффициент разветвления 10) это уже 16 мА. Эти 16 мА могут попасть на

землю через проводящий транзистор Тг

Более сложный случай, если выход Z имеет //-состояние и должен

управлять десятью присоединенными элементами. Вытекающий из выхода Z

ток вызывает падение напряжения на Rc. На значение этого напряжения

уменьшается выходной уровень Z. Это неудобно. Уменьшение выходного

уровня можно предотвратить, используя схему на дополнительном

транзисторе, так называемый двухтактный выходной каскад. Такой каскад

представлен на рис. 6.45.

Один из транзисторов Тъ и Т4 должен быть заперт, другой проводить.

Если заперт Тъ и проводит Т4, то на выходе Z действует уровень L.

Поступающий на выход Z ток течет через Т4 на землю.

Если заперт Т4 и проводит Tv то на выходе Z действует уровень Н. Ток

управления, необходимый для следующих элементов, течет от + UB через

R4, Т3, диод D, — к выходу Z. Если выход Z нагружается сильнее,

т. е. через выход ZTe4eT сильный ток, то выходной уровень падает только

на значение падения напряжения на резисторе R4. На Т3 и 2), при

возрастании тока не возникает дополнительного падения напряжения.

Двухтактная схема может выдавать и принимать относительно большие токи.

При переключении выходных состояний оба транзистора Тг и Т4 могут

кратковременно проводить. Сопротивление R4 в этом случае ограничивает

ток.

Диод Dj служит для создания нужного уровня напряжения. Как он понижает напряжение, наглядно показано на схеме на рис. 6.46.

Если транзистор Т2 проводит, то к точке В4 приложено напряжение

примерно 0,7 В (напряжение база-эмиттер Т4). Транзистор Т4 будет

полностью открыт. К точке Z приложено напряжение примерно +0,2 В. К Т2

тоже приложено напряжение коллектор-эмиттер 0,2 В, так что в точке Вг

потенциал относительно земли получается 0,9 В. Без диода Х>, на

транзистор Тъ подавалось бы напряжение базис-эмиттер UBE = 0,7 В

(эмиттер +0,2 В, база +0,9 В). Транзистор Тъ также открылся бы.

Так как на диоде Dx падение напряжения составляет примерно 0,7 В, то

потенциал эмиттера Тъ поднимается до уровня примерно 0,9 В. При этом

UBE транзистора Г3 будет равно примерно 0 В, и Тг надежно закрывается.

При переключении от ТТЛ-элементов на выходе получаются довольно крутые

импульсы напряжения. Переходное время сигнала (см. разд. 6.4.3)

достаточно мало и составляет примерно 5 не. Вследствие этого могут

возникнуть так называемые «колебания напряжения».

Переходный процесс при переключении входа ТТЛ-элемента с Яна L

изображен на рис. 6.47. Напряжение на входе может доходить

кратковременно до —2 В. Диоды Dv D3 и D4 в схеме на рис. 6.46

должны подавлять колебания напряжения и принимать на себя отрицательное

напряжение. Они называются отводными диодами.

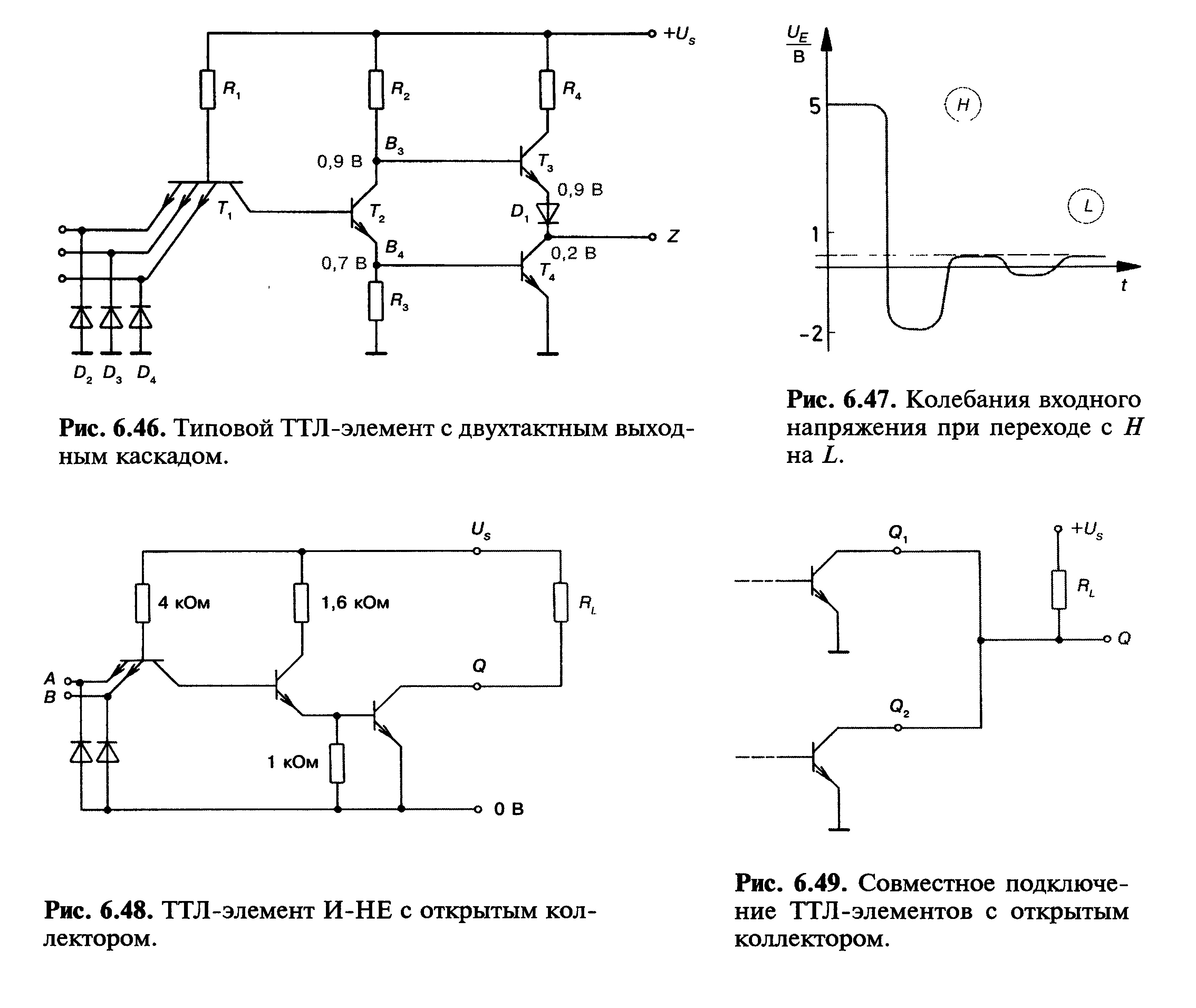

В TTJI-схемах имеются элементы с так называемым «открытым

коллектором». В этих элементах отсутствует сопротивление

коллектора. Вывод коллектора подключен к выводу на корпусе элемента

(рис. 6.48).

При синтезе схем следует правильно подбирать сопротивление коллектора.

Элементы с открытым коллектором предназначены для проводных операций.

Можно соединить открытые коллекторы нескольких элементов вместе и затем

общую точку соединить с источником питания (рис. 6.49). Величина

совместного сопротивления выбирается согласно рекомендациям

производителя. При этом большое значение имеет число совместно

подключенных элементов.

Представленная на рис. 6.49 схема является схемой проводного И при

положительной логике. Если выход имеет уровень L, т. е. выходной

транзистор открыт, то общая точка Q будет всегда на уровне L. Только

если все выходные транзисторы заперты, или все выходы имеют //-уровень,

общая точка имеет //-уровень.

ТТЛ-семейство делится на ряд более мелких подсемейств. Схемы отдельных

подсемейств различаются между собой прежде всего потреблением мощности

и быстродействием, а также помехоустойчивостью.

Похожие статьи