Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

ДТЛ-схемы

Введение

ДТЛ-схемы реализуются на диодах и транзисторах. Конечно, дополнительно применяются и сопротивления. Термин ДТЛ произошел от английского «Diode Transistor Logic» и переводится как «диодно-транзисторная логика». Схемы этого семейства сначала строились на отдельных элементах, а затем в виде тонкопленочных и толстопленочных (интегральных) микросхем (см. Бойт, Электроника, часть 2). В настоящее время они производятся почти исключительно в виде монолитных микросхем.

Основные ДТЛ-схемы

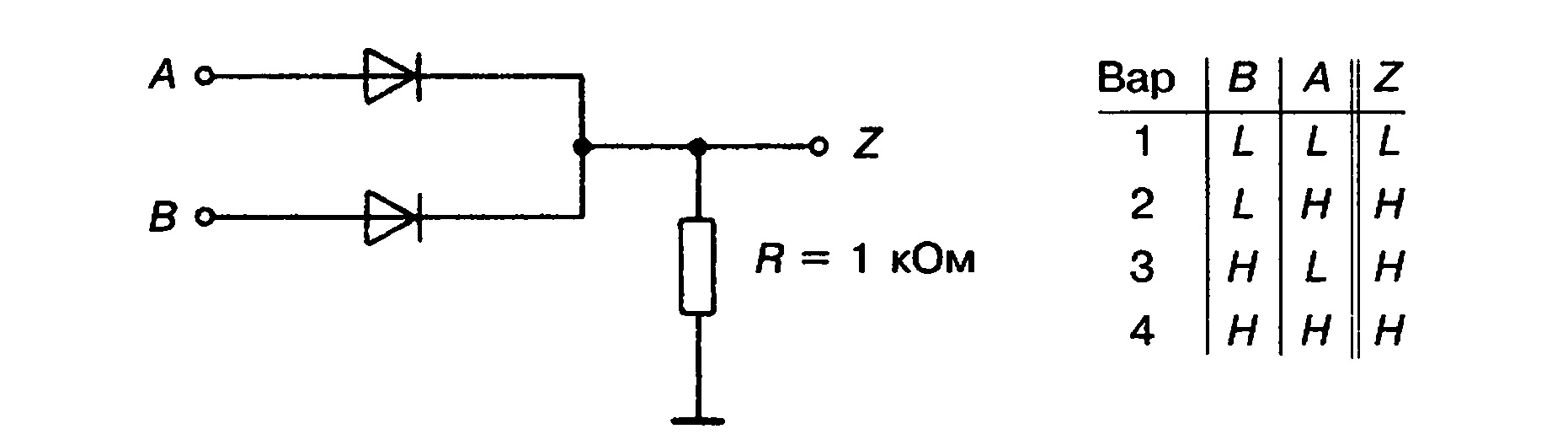

Одна из трех основных схем семейства ДТЛ показана на рис. 6.28. С этой схемой мы уже познакомились в разд. 6.2. Если хотя бы на одном из входов присутствует ВЫСОКИЙ уровень Н (высокий положительный потенциал, от англ. High — высокий), то он будет действовать и на выходе. При положительной логике схема работает как логический элемент ИЛИ.

Рис. 6.28. ДТЛ-схема (ИЛИ-элемент при положительной логике)

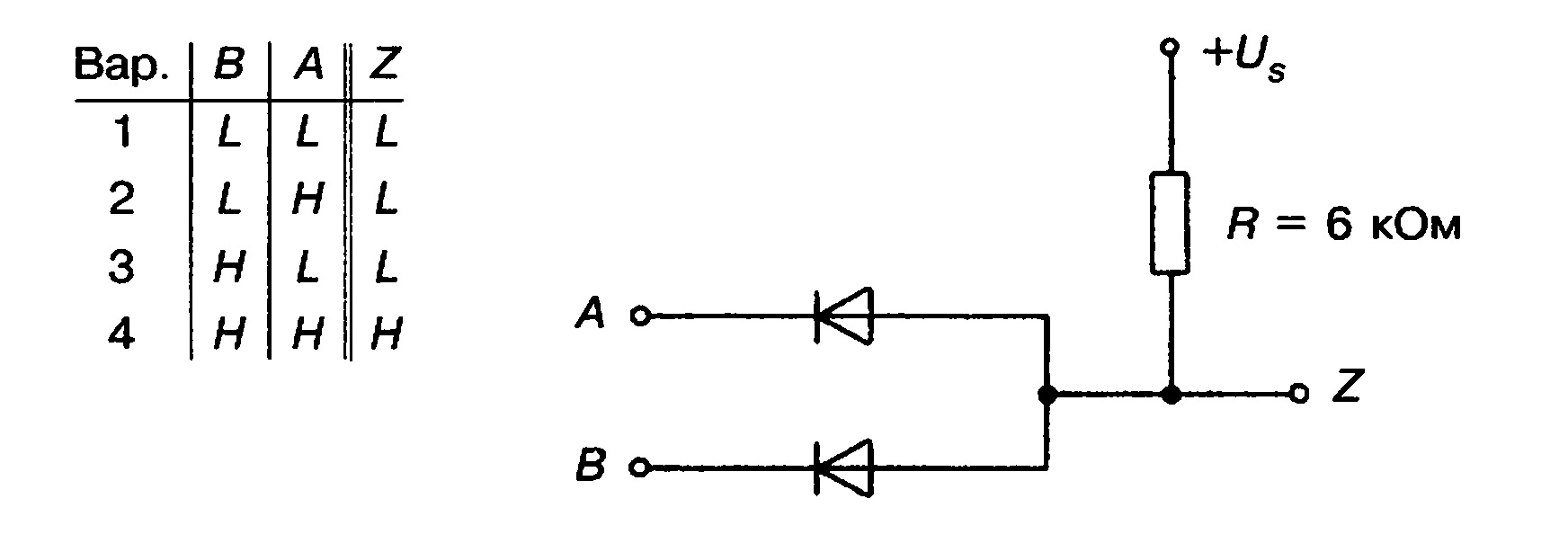

В схеме, изображенной на рис. 6.29, ВЫСОКИЙ уровень на выходе вентиля сформируется только в том случае, если он будет присутствовать на обоих входах. Если на каком-либо его входе будет НИЗКИЙ уровень L (например нулевой потенциал, заземление, от англ. Low — низкий), то он будет действовать и на выходе.

Рис. 6.29. ДТЛ-схема (И-элемент при положительной логике)

Разберем подробнее схему на рис. 6.29. Допустим, что напряжение питания

Us равно 6 В. Напряжение +6 В относится к зоне ВЫСОКИХ уровней. Зона

НИЗКИХ уровней (Z-зона) находится около 0 В (заземление). Если на обоих

входах присутствует ВЫСОКИЙ уровень Н, то диоды заперты, следовательно,

на выходе Z также будет присутствовать ВЫСОКИЙ уровень (от +US через R).

Если теперь на вход В подать НИЗКИЙ уровень (= 0 В), диод в ветви В

откроется. Ток от источника +US потечет через резистор R и диод к

нулевому потенциалу (заземлению). Величина падения напряжения на диоде

составит +0,7 вольта (для кремниевого диода). Такое же напряжение будет

приложено к выходу Z. Это значение напряжения относится к зоне НИЗКИХ

сигналов.

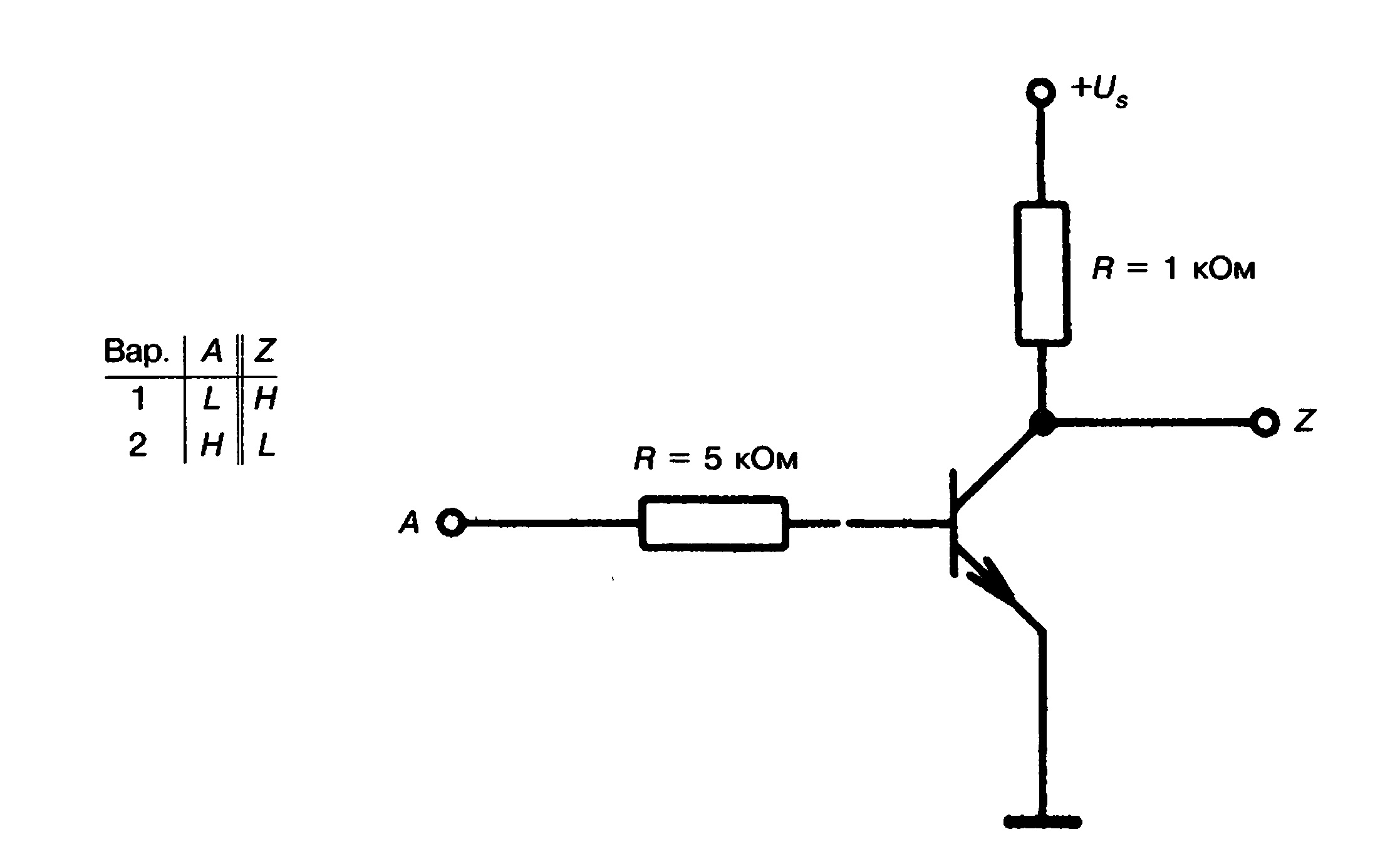

Рис. 6.30. ДТЛ-схема (НЕ-элемент)

Таким образом, выход Z имеет НИЗКИЙ уровень тогда, когда НИЗКИЙ

уровень действует на одном из входов. Только если на обоих входах

присутствует ВЫСОКИЙ уровень, на выходе Z будет ВЫСОКИЙ уровень. Таким

образом, при положительной логике схема работает как логический элемент

И.

Схема на рис. 6.30 работает как инвертор, то есть логический элемент

НЕ. Если на входе А действует ВЫСОКИЙ уровень, то транзистор открыт. К

выходу Z прикладывается напряжение 0,2—0,3 В, которое

соответствует НИЗКОМУ уровню. Если на входе А действует НИЗКИЙ уровень,

то транзистор запирается. Сопротивление эмиттер-коллектора высокоомно

(например, 10 МОм) и почти все напряжение питания прикладывается к

выходу, имеющему таким образом ВЫСОКИЙ уровень. Соответствующая таблица

истинности представлена на рис. 6.30.

Как ведет себя вход, к которому не приложен ни ВЫСОКИЙ (~ +6 В), ни НИЗКИЙ (= 0 В, заземление) уровень?

На схеме (рис. 6.28) такой открытый вход действует как НИЗКИЙ уровень.

При этом на выходе может быть ВЫСОКИЙ уровень только тогда, когда

ВЫСОКИЙ уровень действует на одном из входов.

Если вход инвертора, изображенного на схеме 6.30, открыт, то это

эквивалентно прикладыванию на вход НИЗКОГО уровня. Ведь транзистор не

может проводить с неподключенной базой.

Если открытым остается вход схемы на рис. 6.29, то это соответствует

приложению ко входу ВЫСОКОГО уровня. При открытом входе выход не может

принять НИЗКИЙ уровень. Если вход А остается открытым, а на входе В

действует ВЫСОКИЙ уровень, то на выходе также действует ВЫСОКИЙ уровень

Н. Логические элементы ИЛИ (см. рис. 6.28) и И (см. рис. 6.29) являются

при положительной логике пассивными элементами, т. е. они не содержат в

себе активного элемента (усилителя). Если последовательно соединить

несколько пассивных логических элементов, то существует опасность, что

уровни напряжения выйдут из допустимых областей. Прежде всего, может

недопустимо упасть ВЫСОКИЙ уровень. Чтобы избежать этой опасности,

применяют так называемые активные элементы, то есть элементы с

усилителями.

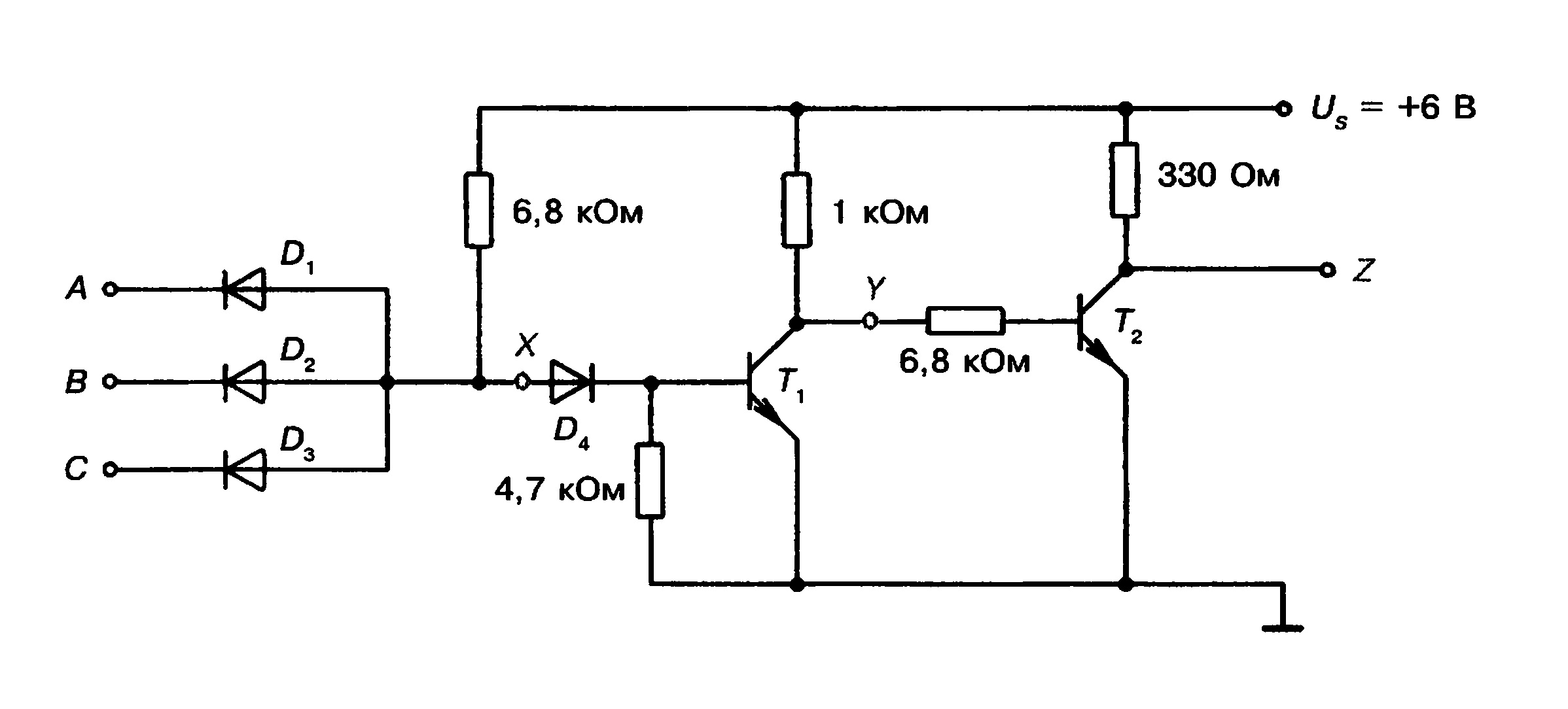

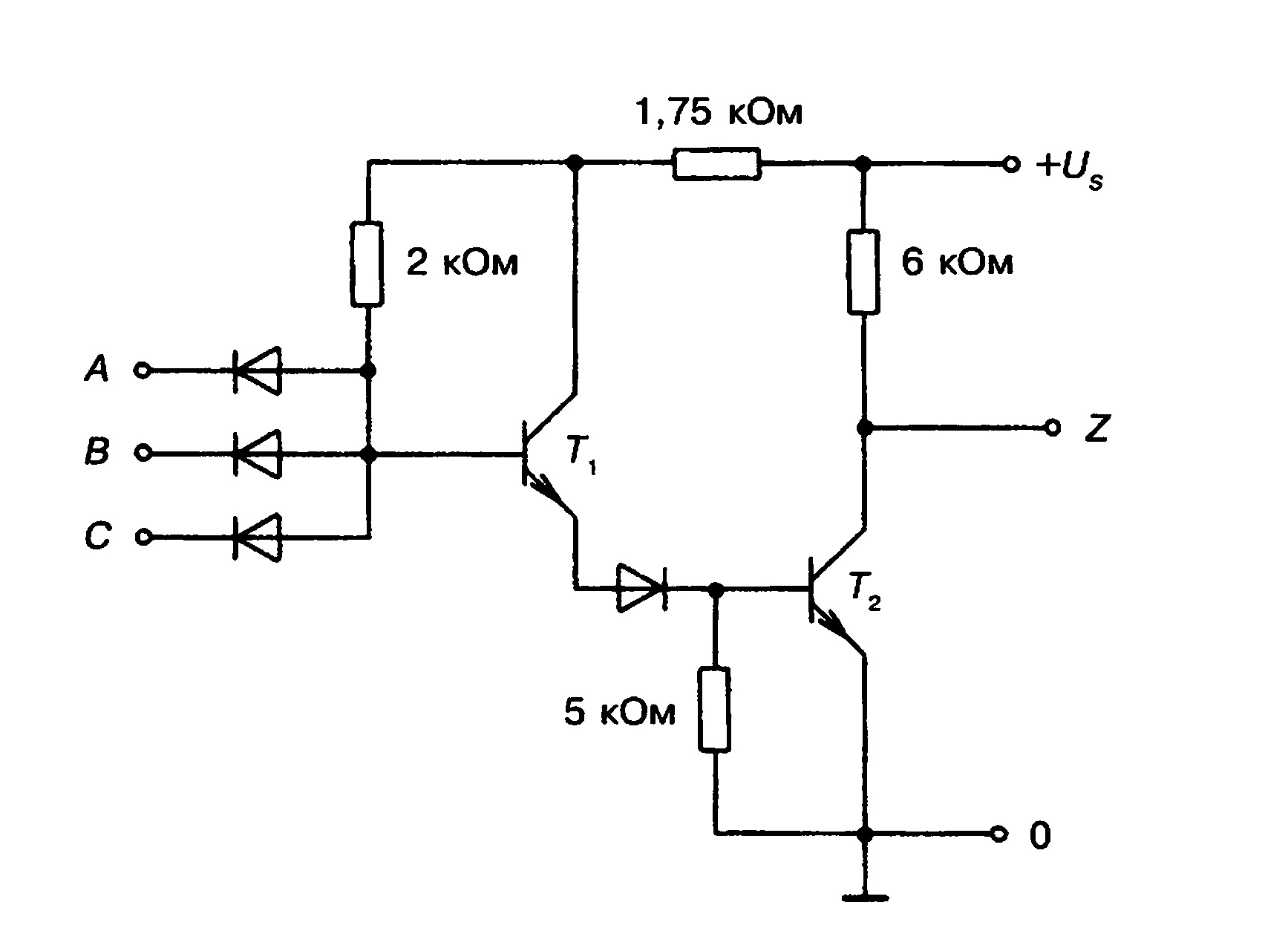

На рис. 6.31 изображен активный логический элемент, который работает в

качестве вентиля И при положительной логике. В точке X находится

Рис. 6.31. ДТЛ-схема (активный И-элемент при положительной логике)

И-сумматор. Затем подключен инвертор с выходом Y, за которым следует еще один инвертор с выходом Z. Оба последовательно включенных инвертора компенсируют действие друг друга, так что на выходе Z снова оказывается сигнал сумматора И. Таблица истинности для данной схемы при положительной логике приведена на рис. 6.32.

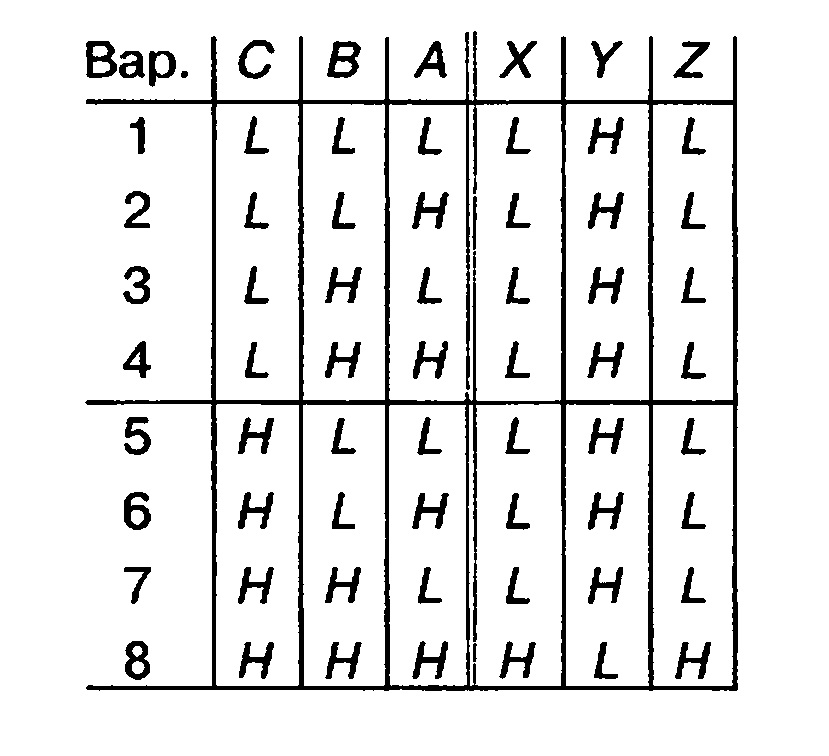

Рис. 6.32. Рабочая таблица к схеме рис. 6.31.

Задачей диода Z>4 является недопущение отпирания транзистора Т1

при открытых диодах входной цепи или при НИЗКОМ уровне на их входах,

когда к точке X приложено пороговое падение напряжения на входных

диодах (= 0,7 В). В отсутствие диода это напряжение могло бы привести к

отпиранию транзистора Тг Этот диод называют сдвигающим уровень

(сдвиговые диоды). При его введении для открытия транзистора необходимо

иметь в точке ^минимальное напряжение примерно 1,4 вольта (= 0,7 В

пороговое падение напряжения на диоде D4 и = 0,7 В пороговое напряжение

база-эмиттер транзистора 71,).

Если в схеме на рис. 6.31 убрать один из инверторов, то при

положительной логике получается логический элемент «И-НЕ».

Интересная схема логического элемента «И-НЕ» ДТП изображена

на рис. 6.33. Транзистор Тх работает как эмиттер, то есть усилитель без

инвертирования. За усилителем подключен инвертор. Такая ДТЛ-схема (рис.

6.33) применяется особенно часто.

Для обзора имеющихся в настоящее время в продаже ДТЛ-схем следует

обратиться к каталогам фирм-производителей. ДТЛ-схемы предлагаются в

стандартном исполнении с напряжениями питания от 5 до 6 В (например от

Valvo).

Схемы семейства ДТЛ отличаются относительно высоким быстродействием.

Быстродействие характеризует время реакции логического элемента на

изменение сигналов на входах и составляет для ДТЛ-элементов примерно 30

не (10~9 с). Однако элементы ТТЛ-семейства (см. разд. 6.6) работают в

три раза быстрее. Их быстродействие составляет около 10 не. Это значит,

что ДТЛ-элементы чаще всего применяют там, где не предъявляются

особенно высокие требования к быстродействию.

Рис. 6.33. ДТЛ-схема («И-НЕ»-элемент при положительной логике)

Преимуществом ДТЛ-схем перед ТТЛ-схемами является их более высокая помехоустойчивость.

Ниже приведены типичные характеристики для ДТЛ-схемы, изображенной рис. 6.33:

Похожие статьи