Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

ТТЛШ с пониженным энергопотреблением (Low-Power ТТЛШ)

Элементы подсемейства ТТЛШ потребляют меньше энергии при увеличении сопротивлений в токовых контурах. Мы уже отмечали этот эффект при рассмотрении подсемейстаа ТТЛ с пониженным энергопотреблением (разд. 6.6.3).

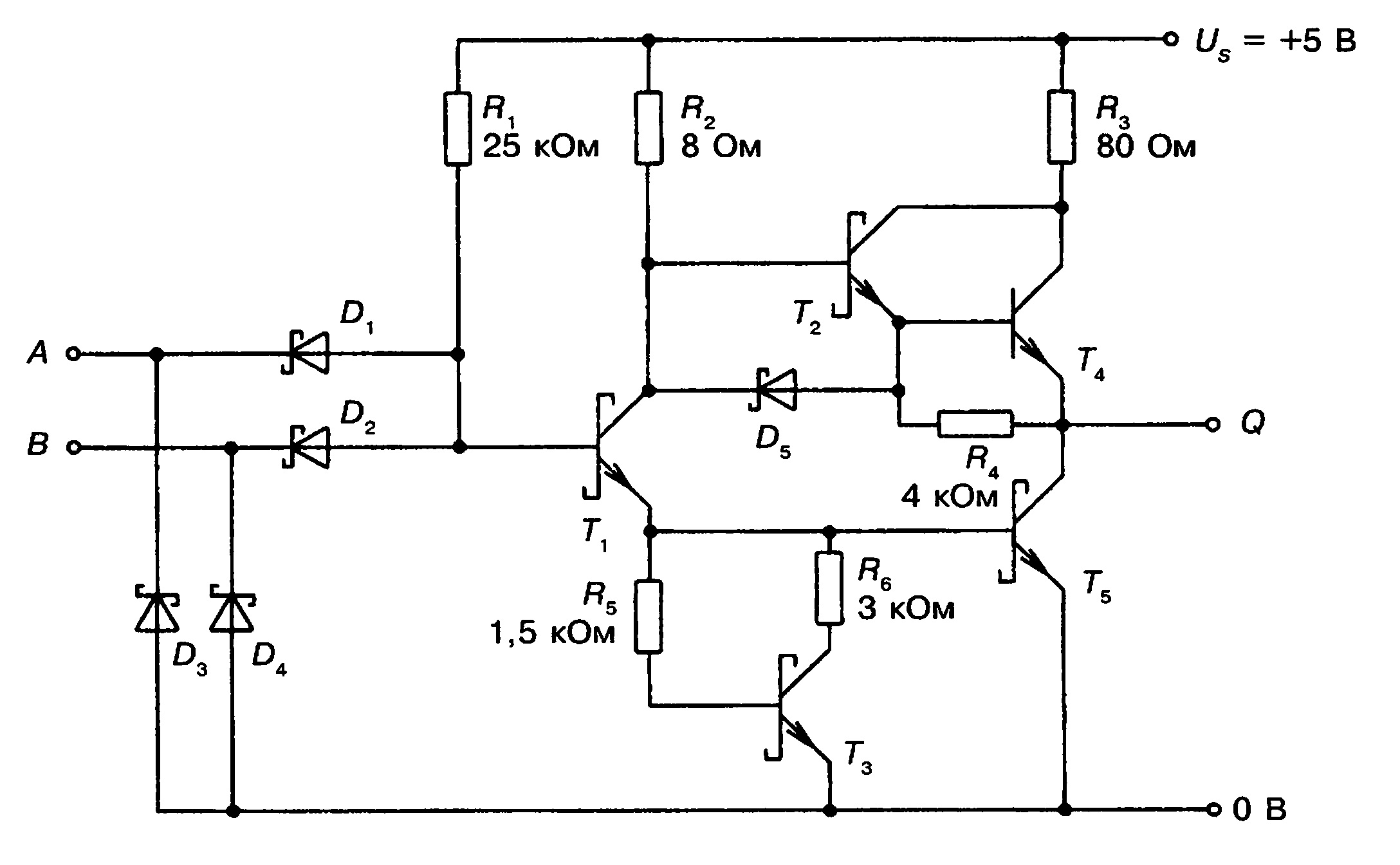

Рис. 6.76. Элемент ТТЛШ 74 LS 00 (Texas Instruments)

При увеличении сопротивлений время заряда-разряда емкостей

транзистора возрастает и, следовательно, быстродействие ТТЛШ с

пониженным энергопотреблением понижается.

Структура ТТЛШ с пониженным энергопотреблением совпадает со структурой

обычных ТТЛШ. Только сопротивления берутся больше. На рис. 6.76

изображена схема типичного ТТЛШ с пониженным энергопотреблением.

Среднее время задержки tp составляет 9,5 не, энергопотребление —

2 мВт.

Быстродействие ТТЛШ с пониженным энергопотреблением и обычных ТТЛШ

практически одинаковы. При этом они потребляют только 1/5 энергии

обычных ТТЛШ.

Недостатком обоих подсемейств ТТЛШ, обычного и с пониженным

энергопотреблением, является низкая помехоустойчивость по сравнению со

стандартными ТТЛ.

Похожие статьи