Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Положительная и отрицательная логика

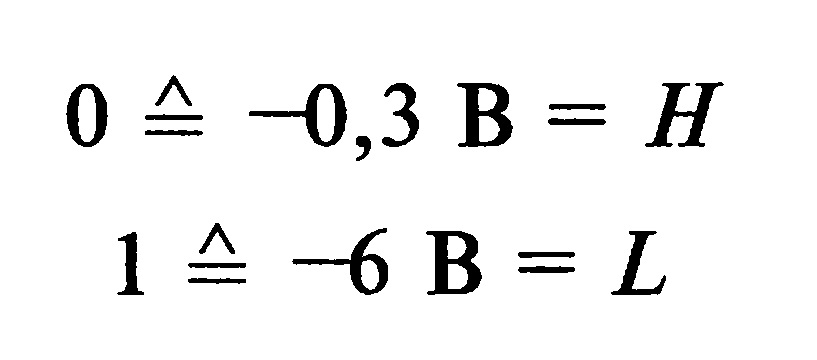

«ВЫСОКИЙ» и «НИЗКИЙ» уровни L и H могут соответствовать логическим состояниям 0 и 1 двумя различными способами:

Если состояние 1 определяет ВЫСОКИЙ уровень, а состояние 0 определяет НИЗКИЙ уровень, то такая логика называется положительной.

В современной цифровой технике работают преимущественно с положительной

логикой. Если к схеме нет соответствующего примечания, считается, что

она использует положительную логику.

Если состояние 1 определяет НИЗКИЙ уровень, а состояние 0 определяет ВЫСОКИЙ уровень, то такая логика называется отрицательной.

Пример ----------------------------------------------------------------

Отрицательная логика имела большое значение во времена существования

только одних PNP-транзисторов. При отрицательном напряжении UCE на

выходе транзисторного каскада получалось отрицательное напряжение.

О 4 -0,3 В = Н 1 4 -6 В = L

Отрицательная логика используется сегодня только в специальных схемах из соображений помехоустойчивости.

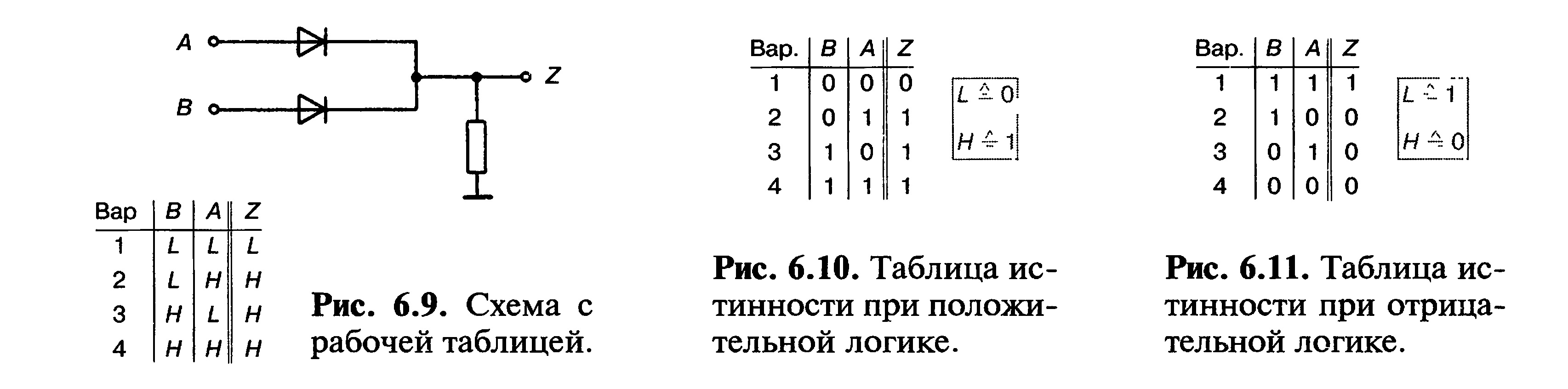

Какие логические операции производит схема на рис. 6.3 при положительной логике, а какие — при отрицательной?

Схема и соответствующая рабочая таблица представлены на рис. 6.9. Из

рабочей таблицы определяется таблица истинности. При положительной

логике ВЫСОКИЙ уровень Н определяет логическое состояние 1, а НИЗКИЙ

уровень L — логическое состояние 0 (рис. 6.10). При положительной

логике схема производит логическое сложение ИЛИ.

При отрицательной логике ВЫСОКИЙ уровень Я определяет логическое

состояние 0, а НИЗКИЙ уровень L — логическое состояние 1 (рис.

6.11). Схема производит логическое умножение И. В таблице истинности

меняется лишь последовательность вариантов.

При переходе от положительной логики к отрицательной и наоборот меняется тип логической операции.

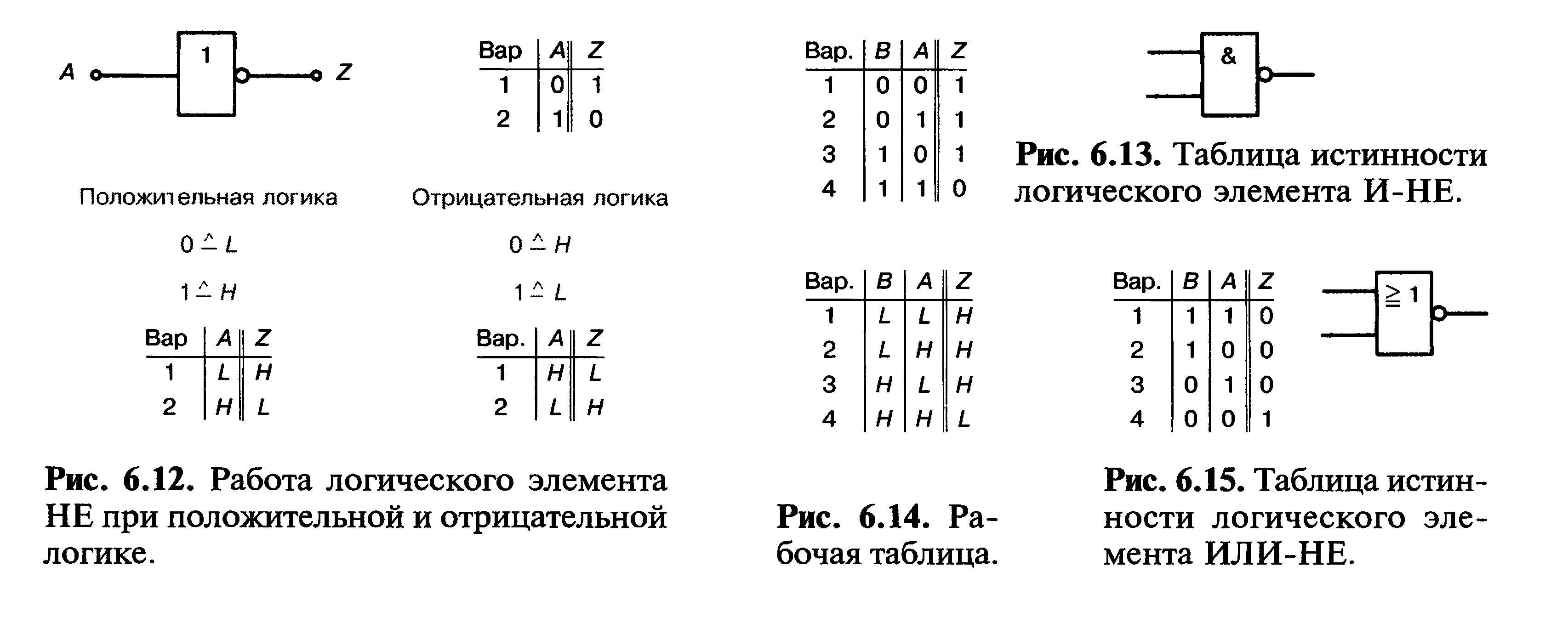

Логический элемент НЕ всегда работает как инвертор — и при положительной, и при отрицательной логике (рис. 6.12).

Пример ----------------------------------------------------------------

Схема работает при положительной логике как элемент И-НЕ. Какую логическую операцию производит схема при отрицательной логике?

Таблица истинности элемента И-НЕ представлена на рис. 6.13. Из нее

можно определить рабочую таблицу с уровнями Ни L. При положительной

логике ВЫСОКИЙ уровень Я определяет логическое состояние 1, а НИЗКИЙ

уровень L — логическое состояние 0 (рис. 6.14).

Работа схемы при отрицательной логике показана в таблице истинности на

рис. 6.15. Она получилась из рабочей таблицы, в которой теперь ВЫСОКИЙ

уровень Н определяет логическое состояние 0, а НИЗКИЙ уровень L —

логическое состояние 1.

Получается логическая операция ИЛИ-НЕ.

Схема, которая при положительной логике выполняет операцию И-НЕ, при отрицательной логике выполняет операцию ИЛИ-НЕ.

Похожие статьи