Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Триггер на элементах «И-НЕ»

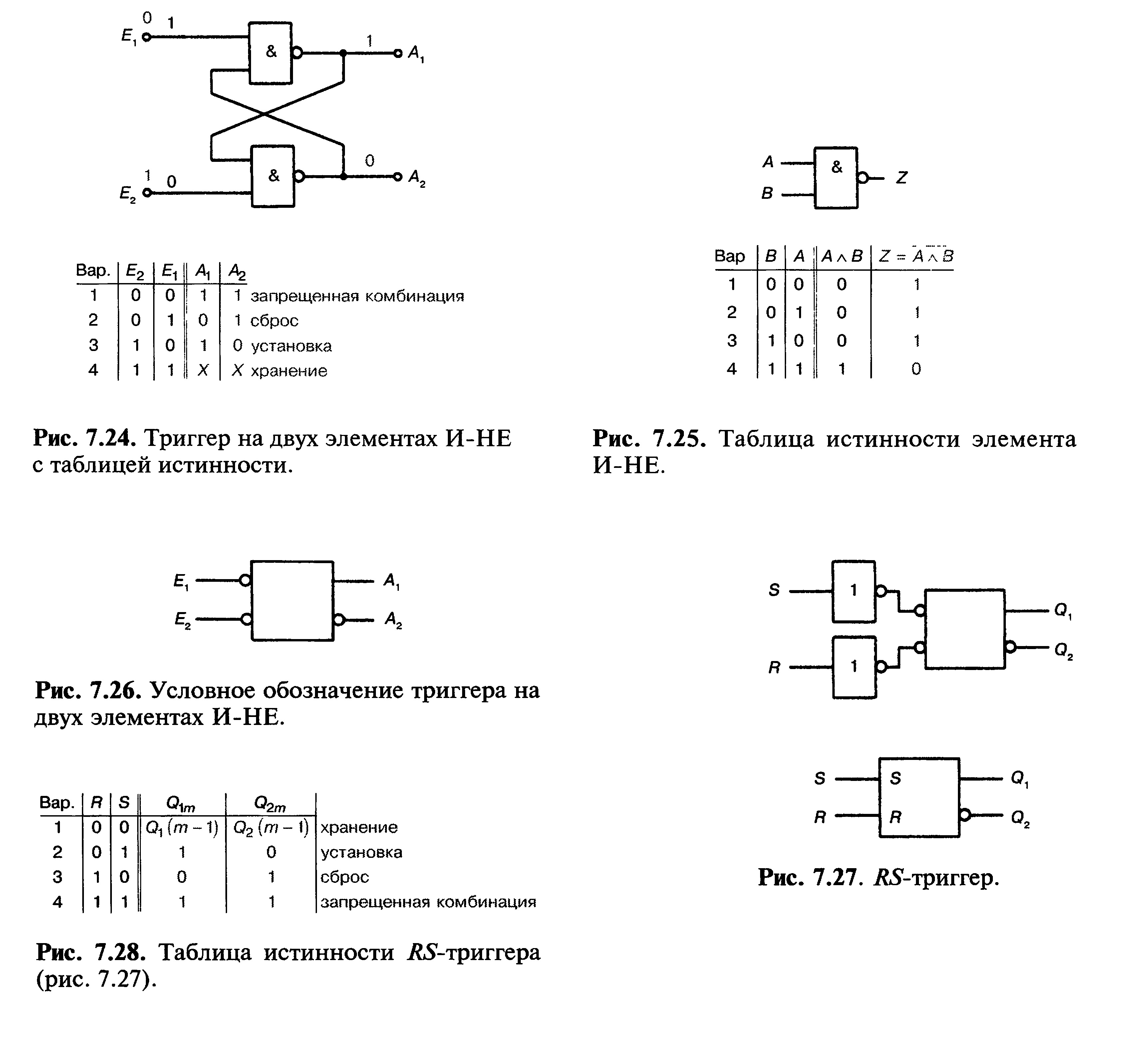

Если соединить два элемента «И-НЕ» последовательно, как это изображено на рис. 7.24, то тоже получится триггер. Посмотрим, как он работает. Для удобства на рис. 7.25 представлена таблица истинности элемента «И-НЕ». Если по меньшей мере на одном входе элемента «И-НЕ» будет нулевой сигнал, то на выходе возникнет логическая 1.

При Ех = 0 и Е2 — 1 на выходе триггера установятся Ах = 1 и А1 = 0. Это режим установки. При Ех = 1 и Е2 — 0 на выходе триггера установятся Ах = 0 и А2 = 1. Это режим сброса. Если на оба входа подана 1, то состояние выходов останется таким же, как и предыдущее, то есть не изменится. Это режим хранения.

Режима, при котором оба входа Еу и Ег равны нулю, следует избегать. В этом режиме оба выхода должны установиться в 1. Триггер из двух элементов «И-НЕ» переключается 0-сигналами.

Сказанное продемонстрировано условным обозначением триггера на рис. 7.26. Если перед каждым входом включить элемент НЕ, получится ЛУ-триггер (рис. 7.27). Соответствующая таблица истинности изображена на рис. 7.28. Она расширена по сравнению с ранее представленными таблицами истинности. В первом варианте — режиме хранения — добавились QUm _ „и Q2(m Индекс т — 1 обозначает предшествующее состояние выходов. Если Qlm = Ql(m _ 0 и Qlm = Q1(m _ I}, значит, состояния выходов в текущий момент времени (Qlm, Q2m) равны предшествующим состояниям (QHm_l), Q1(m_,)). Так однозначно обозначается режим хранения.

Триггеры на рис. 7.21 и рис. 7.24 являются самыми простыми триггерами. Они поэтому называются еще базовыми триггерами.

Похожие статьи