Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

JK-триггеры, управляемые по одному фронту

В поисках максимально универсального триггера за основу был взят управляемый по одному фронту ^-триггер. Универсальный триггер должен иметь режимы хранения, установки и сброса ^-триггера (см. таблицу истинности на рис. 7.53). В случае запрещенной комбинации 4 с 5 = 1 и й = 1 триггер должен переключаться как Г-триггер.

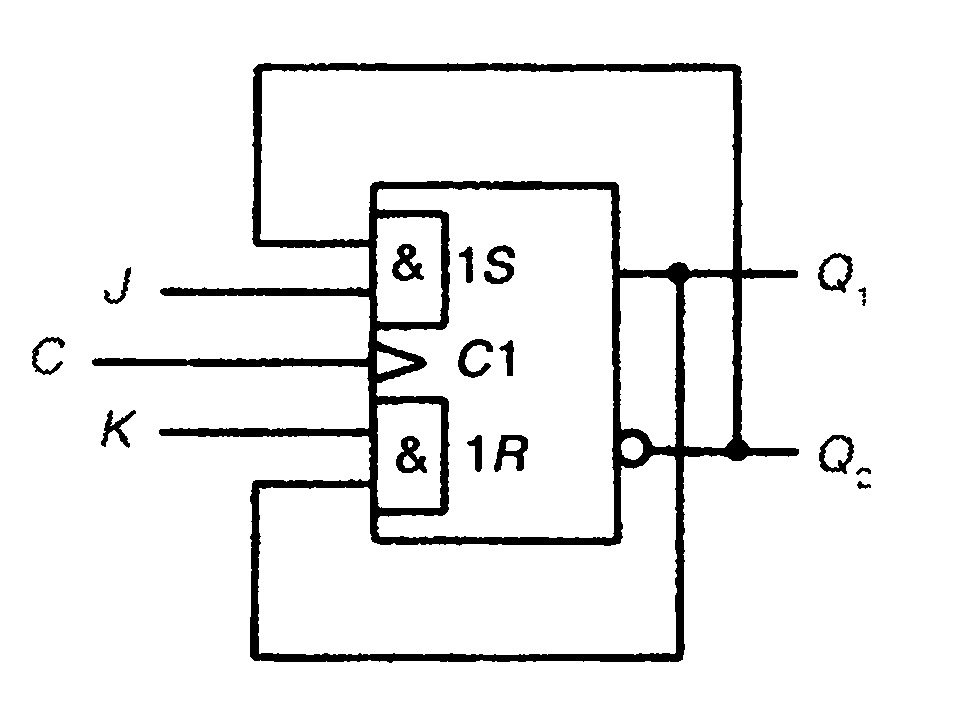

Такой универсальный триггер мы уже нашли, он изображен на схеме (рис. 7.63). Надо только снова восстановить связь 5-входа и Л-входа с Г-входом (рис. 7.64). Новые входы называются / и К.

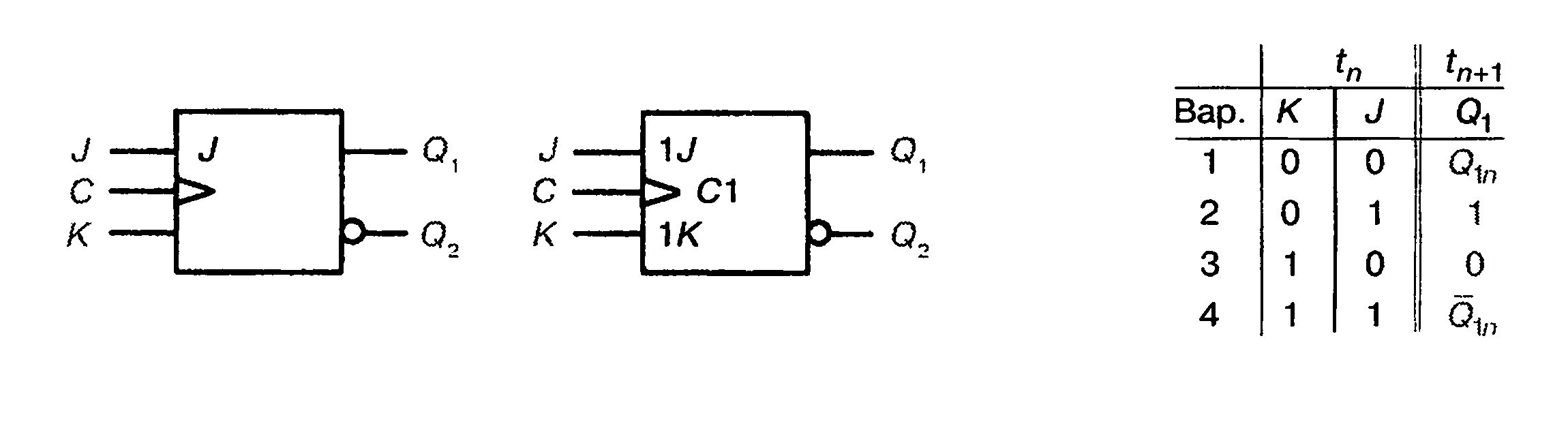

При комбинации / = 0 и К = 0 триггер работает в режиме хранения. При / = 1 он устанавливается, если Q, = 0 и Q2 = 1. Сброс происходит при К= 1, когда Q, = 1 и Q2 = 0, все переходы, разумеется, фронтально-управляемые. При /= 1 и К= 1 триггер ведет себя как Г-триггер.

Обозначения / и К взяты произвольно из алфавита и не являются каким-либо сокращением. Условное обозначение управляемого по фронту /А'-триггера вместе с таблицей истинности приведены на рис. 7.65.

Рис. 7.64. Образование JK-триггера из RS-триггера

Рис. 7.65. Условное обозначение и таблица истинности управляемого по одному фронтуJK-триггера (управление по переднему фронту).

Конечно, существуют также /^-триггеры, управляемые задним фронтом импульса. Большинство /АГ-триггеров имеют несколько входов и несколько выходов, которые связаны логическим умножением И.

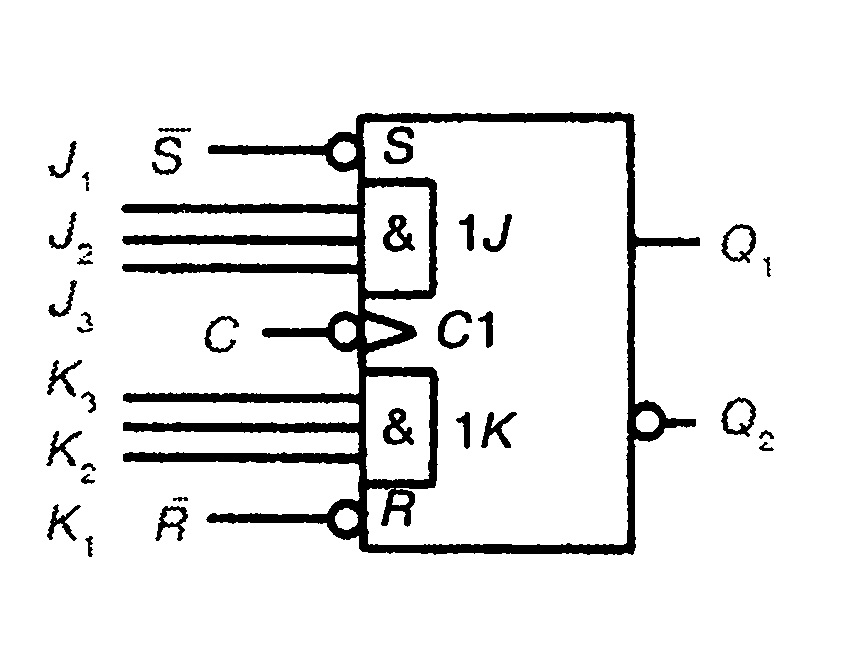

Также часто на триггерах используются нетактируемые входы установки и сброса. На рис. 7.66 показано условное обозначение такого /ЛТ-триггера. Нетактируемые входы установки и сброса переключаются 0-сигналами,

поэтому они обозначаются S и R.

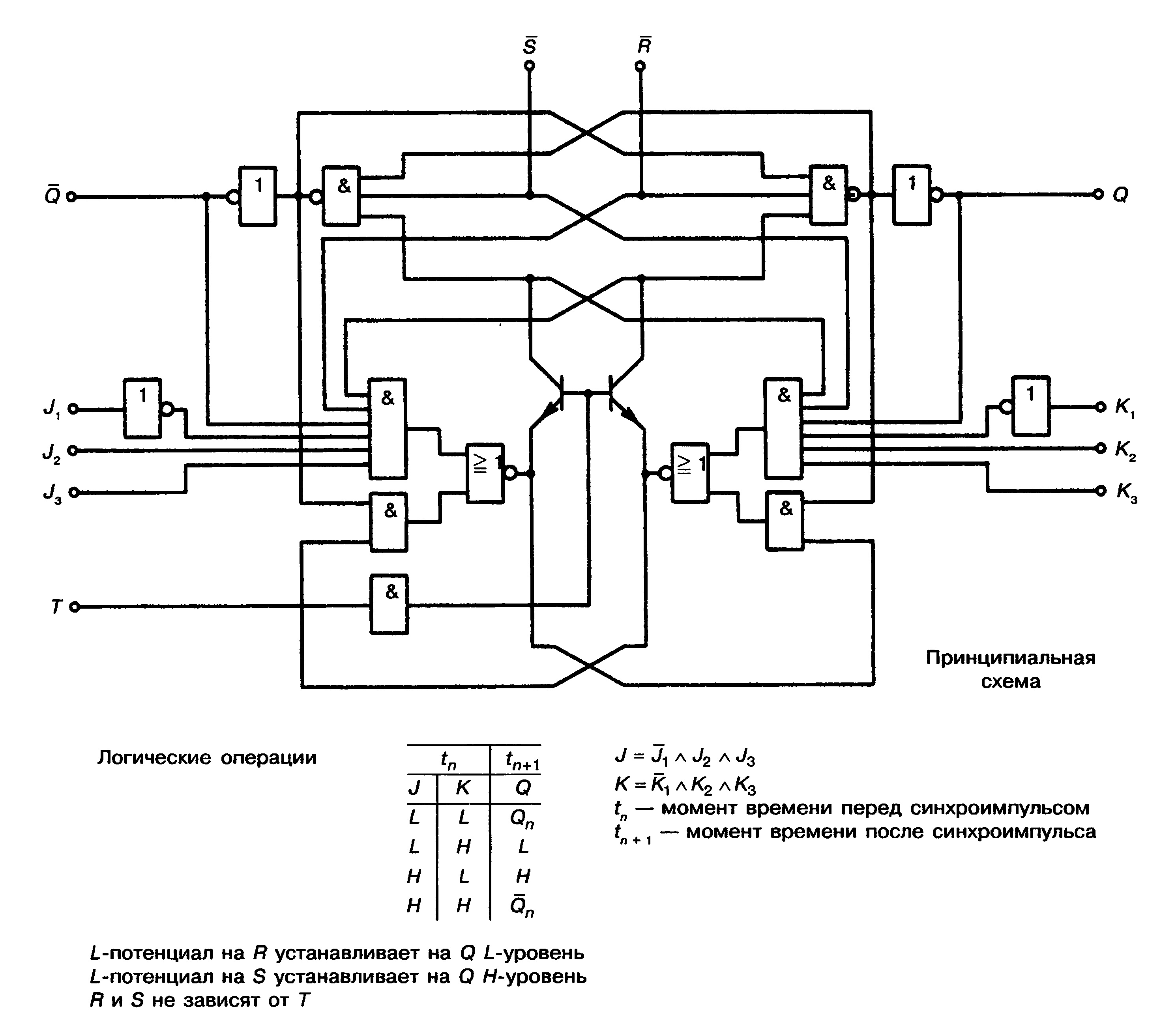

Рис. 7.66. Условное обозначение управляемого по одному фронту JK-триггера с 3 /- и 3 K-входами, нетактируемым входом установки и нетактируемым входом сброса

Элемент FLJ 101/105 является управляемым по фронту

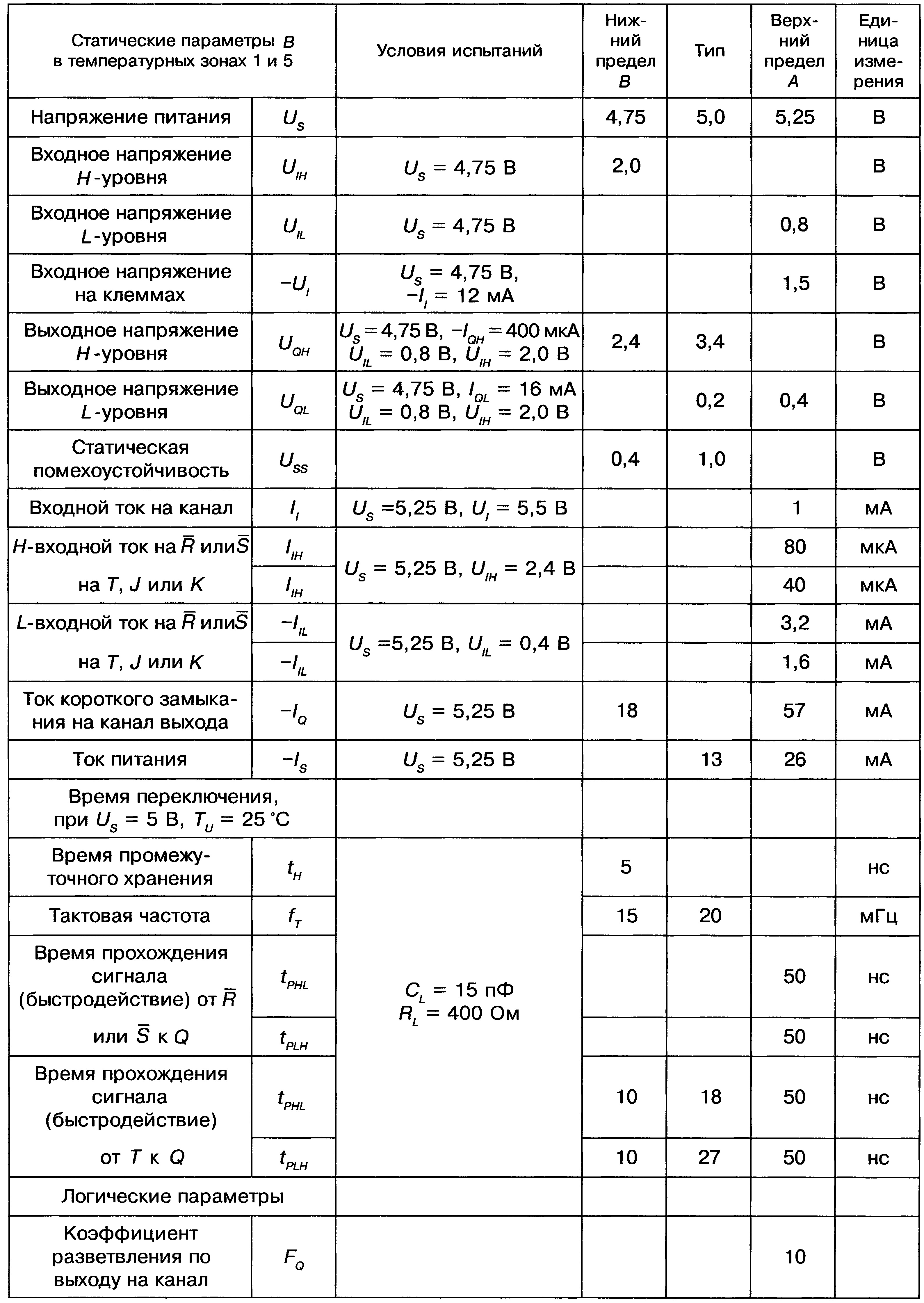

Рис. 7.67. Таблица данных микросхемы FLJ 101-7470

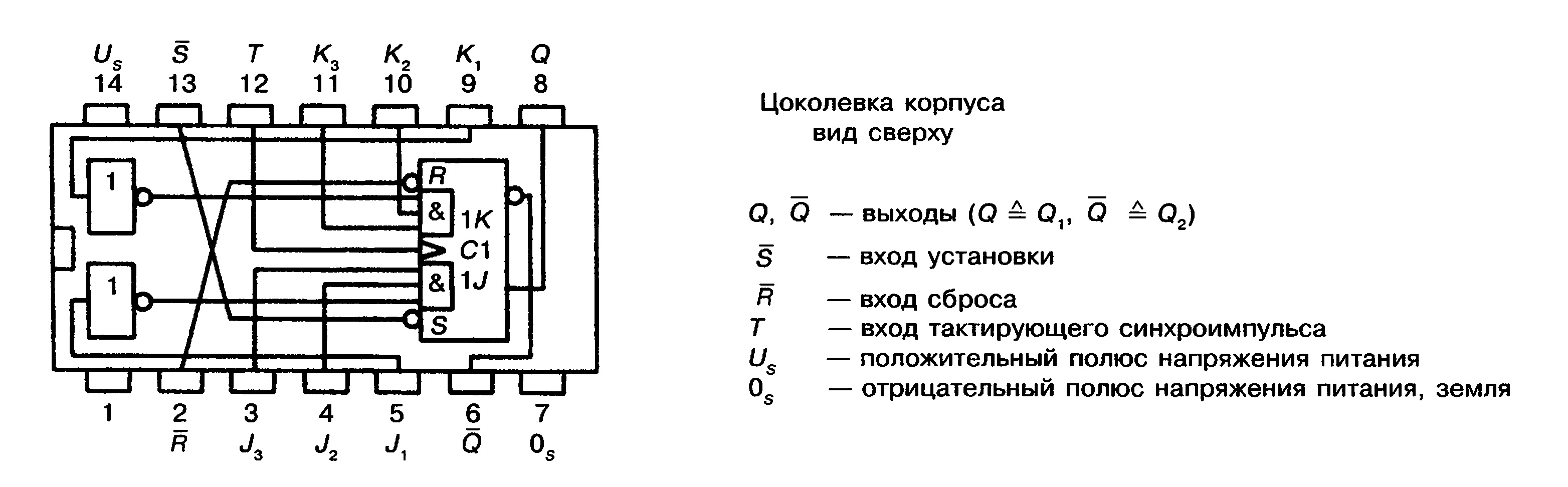

На рис. 7.67 приведена таблица данных микросхемы FLJ 101-7470. Эта микросхема содержит /АТ-триггер с 3 J- и 3 К-входами, нетактируемым входом установки и нетактируемым входом сброса. По цоколевке на рис. 7.68 видно, что входы Ку и /, управляются 0-сигналами.

Рис. 7.68. Цоколевка микросхемы FU 101-7470

Микросхема FLJ 101-7470 принадлежит к TTJl-семейству. Это семейство микросхем рассмотрено в подразд. 6.6.2.2. В данном разделе дополнительно вводится так называемое время промежуточного хранения. После подачи высокого уровня синхроимпульса (типичное значение 1,5 В для ТТЛ-схем) входные сигналы должны сохранять свое состояние в течение определенного времени. Это время называется временем промежуточного хранения. По истечении времени промежуточного хранения (обычно 5 не) изменения входного сигнала не имеют значения. Паразитные сигналы могут повлиять на триггер только в течение времени промежуточного хранения. Следовательно, чем меньше время промежуточного хранения, тем более помехоустойчивой является схема.

Как дополнение к таблице данных приводятся блок-схема и таблица уровней (рис. 7.69). В таблице уровню L соответствует 0-сигнал и уровню Н 1-сигнал. Не тактируемые входы установки и сброса обозначаются S и R. Это значит, что эти входы управляются 0-сигналами.

Управляемые по одному фронту /А’-триггеры часто имеют так называемую динамическую память. Она увеличивает время распространения сигнала и предотвращает установку выходов в желаемое состояние еще во время переднего фронта импульса сигнала синхронизации или в течение времени промежуточного хранения. Это могло бы привести к ложному срабатыванию. Рассмотрим управляемый по одному фронту /А'-триггер, который управляется прямым фронтом синхроимпульса. При J = 1 и К = 1 этот триггер будет переключаться, если синхроимпульс достигнет, например, порогового значения напряжения (+1,5 В). Если желаемые выходные состояния (Qj = 1 и Q2 = 0) очень быстро установятся на выходе, то может произойти повторное срабатывание ((), = 0 и Q2 = 1). Динамическая память состоит из одной или нескольких небольших емкостей, которые перезаряжаются. В качестве этих емкостей могут служить емкости запертых рп-переходов. Такие триггеры правильно следует называть триггерами с двойной памятью.

Рис. 7.69. Приложение к таблице данных микросхемы FLJ 101-7470 (Siemens)

Похожие статьи