Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Расчет логических схем

Общие указания

Для синтеза схем в разд. 5.1 описаны следующие шаги:

1. Описание функции требуемой схемы.

2. Назначение входных и выходных переменных величин и присвоение значений 0 и 1.

3. Составление таблицы истинности.

4. Определение необходимых логических операций.

5. Упрощение и при необходимости преобразование схемы.

Если известна таблица истинности, то теперь целесообразно 4-й этап

начинать с составления нормальной формы ИЛИ. Она будет максимально

упрощена с помощью диаграммы Карно. В конце шага 4 получается

упрощенная логическая функция, по которой можно собирать логическую

цифровую схему.

В шаге 5 проверяется, является ли дальнейшее упрощение найденной с

помощью алгебры логики функции возможным и рациональным. Если да, то

упрощение необходимо провести.

Теперь надо узнать, какие логические элементы имеются в наличии.

Логическую функцию нужно преобразовать так, чтобы она содержала только

имеющиеся логические элементы. Затем можно собирать схему.

Цифровая схема включения и выключения из нескольких мест

С помощью логических элементов требуется синтезировать схему,

которая функционирует как схема включения и выключения из нескольких

мест. Выходное состояние должно меняться только в случае, если меняется

состояние одного из входов. Если оба входа меняют свое состояние, то

выходное состояние измениться не должно. Схема должна быть построена на

элементах ИЛИ-НЕ.

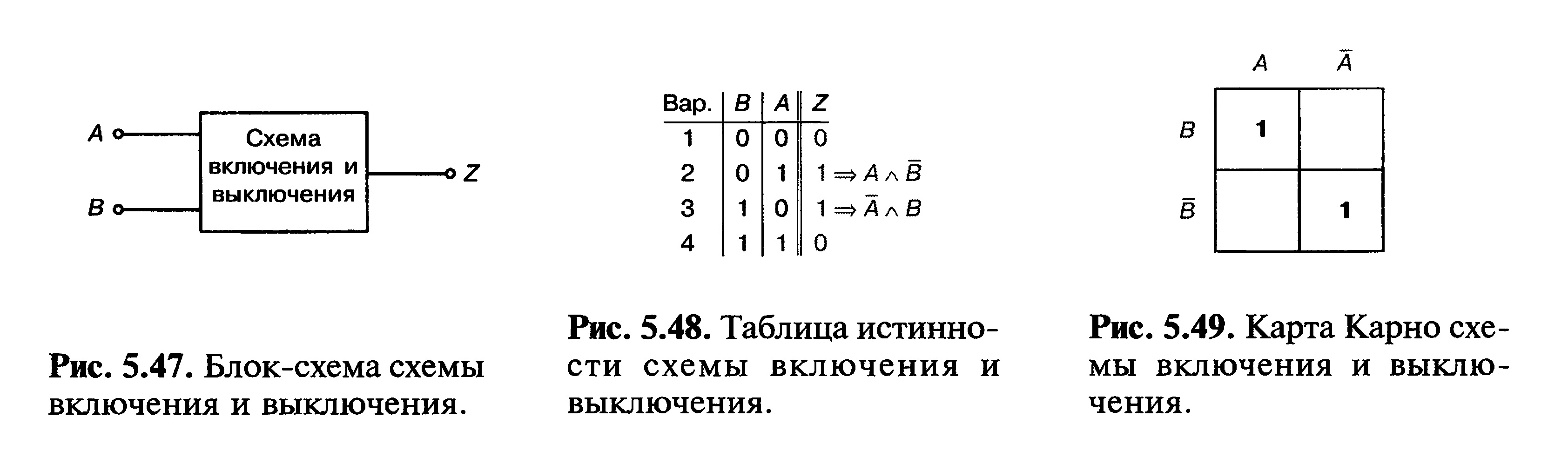

Искомая схема имеет два входа и один выход. Входные переменные

называются А и В. Выходная переменная обозначается Z (рис. 5.47).

Таблица истинности схемы с двумя входными переменными имеет 4 варианта

(рис. 5.48). Исходное состояние Z для первого варианта может

устанавливаться любым образом. Выбрано Z = 0.

При переходе от варианта 1 к варианту 2 переменная А меняет свое

состояние. Переменная В состояние не меняет. Если только один из входов

меняет состояние, то согласно поставленному заданию выход Z должен

поменять свое состояние. Z должен быть равен 1.

При переходе от варианта 2 к варианту 3 переменные А и В меняют свои

состояния. Z не должно измениться. При переходе от варианта 3 к

варианту 4 переменная А меняет свое состояние с 0 на 1. В остается

равной 1. Таким образом, Z должно поменять состояние с 1 на 0. Таблица

истинности готова. Она могла бы выглядеть иначе, если бы мы в варианте

1 выбрали Z= 1.

Для таблицы истинности (рис. 5.48) нужно записать нормальную форму ИЛИ. Она выглядит так:

Z = (AaB)w(AaB).

Если занести нормальную форму ИЛИ в диаграмму Карно, то видно, что дальнейшее упрощение невозможно (рис. 5.49).

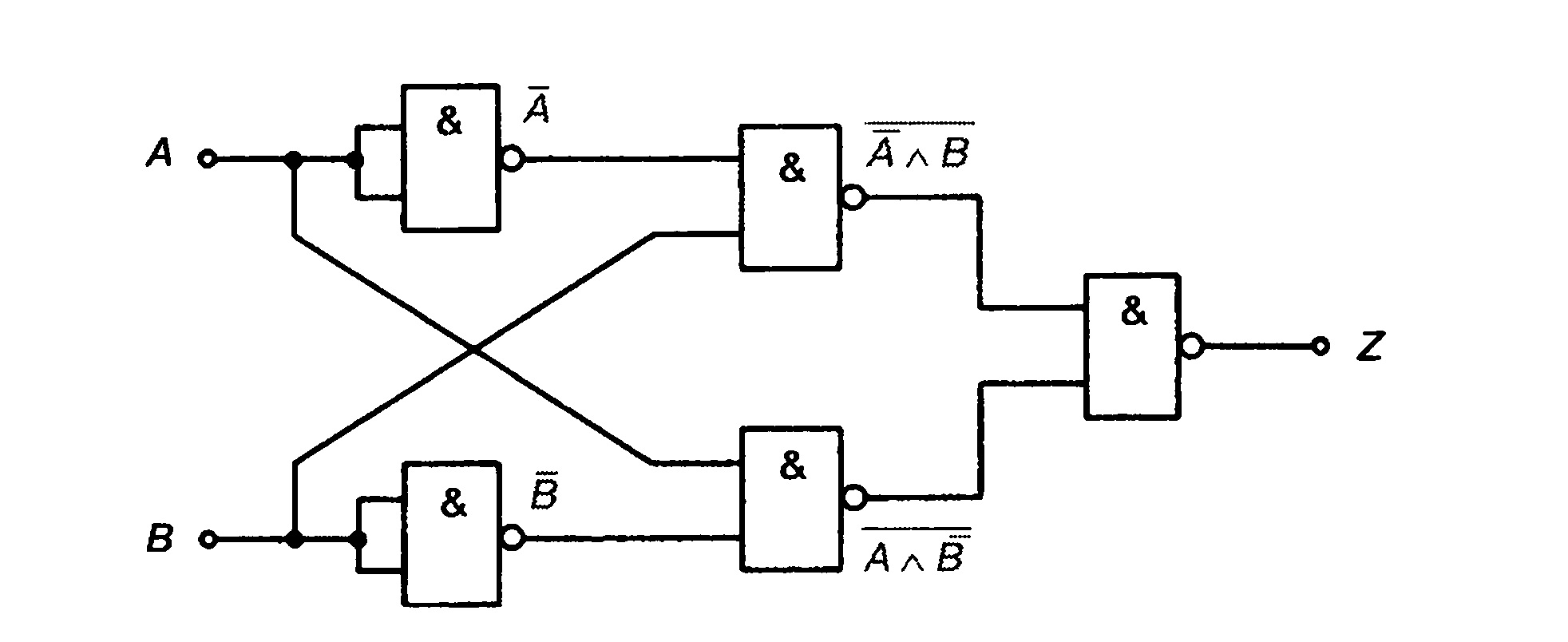

Так как схема должна быть построена на элементах ИЛИ-HE, требуется преобразовать уравнения:

Z = (AaB)w(AaB)-,

Z = (AaB)v(AaB),

Z = АаВаАаВ.

Рис. 5.50 Цифровая схема

Схема, построенная согласно преобразованному уравнению, показана на рис. 5.50.

Переключатель «два из трех»

Системы, связанные с повышенным риском, например атомная

электростанция, должны быть в случае аварии сразу остановлены.

Отключение происходит автоматически, с помощью цифровой схемы. В

аварийных датчиках, ответственных за отключение, могут происходить

ложные срабатывания. Поэтому в каждом критическом месте ставят три

одинаковых аварийных датчика (рис. 5.51).

Отключение должно происходить только тогда, когда сработали по меньшей

мере два аварийных датчика из трех. Такой подход предотвращает ненужные

отключения системы, которые приносят финансовые потери. Аварийные

датчики при срабатывании имеют состояние 1. Отключение системы должно

происходить, если на выходе схемы действует состояние 1.

Итак, требуется схема, выход которой имеет состояние 1 тогда, когда, по

меньшей мере 2 из 3 входов имеют состояние 1. Такая схема называется

переключатель «два из трех».

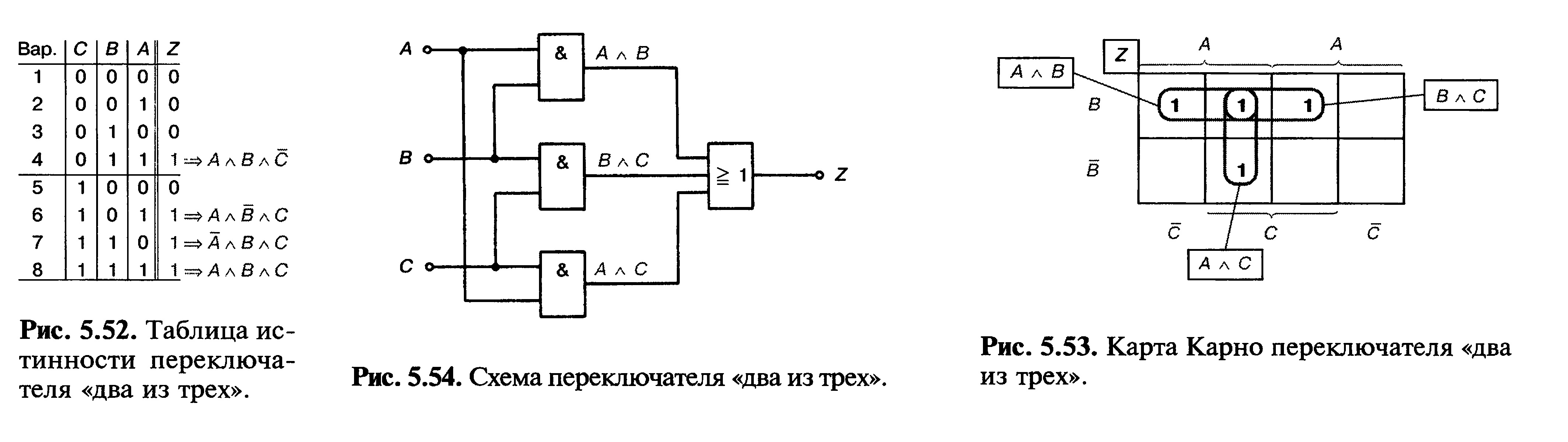

Входные переменные получают имена А, В и С. Выходная переменная —

Z. Составим таблицу истинности по словесному описанию принципа действия

схемы. Всегда, когда две входных переменных равны 1, Z = 1. Если все

три входных переменных равны 1, Z также должна быть равна 1. Такая

таблица истинности показана на рис. 5.52.

Далее по составленной таблице истинности записывается нормальная форма ИЛИ:

Рис. 5.51. Аварийные датчики и схема переключателя «два из трех»

Z = (А а В а С) v (А а В а С) v a5aC|v(^aSaC).

Нормальная форма ИЛИ упрощается с помощью диаграммы Карно (рис.

5.53). Можно образовывать три двойных группы. Упрощенное уравнение

имеет вид:

Z = {AaB)w(BaC)w{AaC).

По этому уравнению можно строить схему (рис. 5.54).

Часто под рукой имеются только эле- А °-менты ИЛИ-HE. Чтобы

построить схему только на элементах ИЛИ-HE, преобразуем уравнение: в

°-

Z = (AaB)v(BaC)v(AaC);

======= С О.

Z = (А л B)v (В aC)v (А лС);

—=====—= Рис. 5.55. Схема переключателя «два

Z = АлВлВлСлАлС. из трех» на элементах Ш1И-НЕ.

Соответствующая схема показана на рис. 5.55.

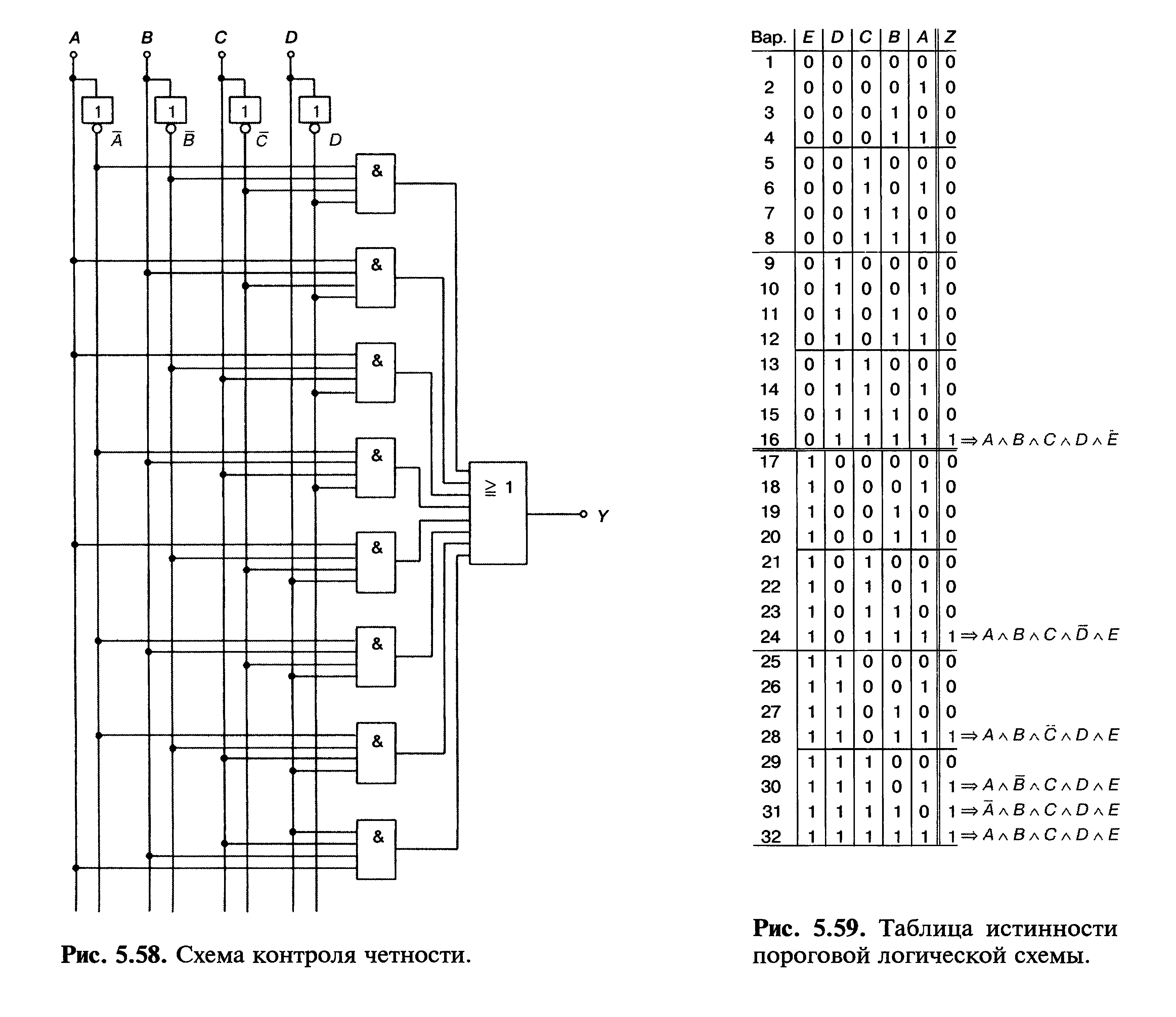

Схема контроля четности

Для обнаружения ошибок в кодах (см. разд. 8.7 и 8.8), а также для

задач контроля и наблюдения часто требуется схема, в которой выход

равен 1 тогда, когда четное число входов имеют состояние 1.

Такая схема называется схемой контроля четности.

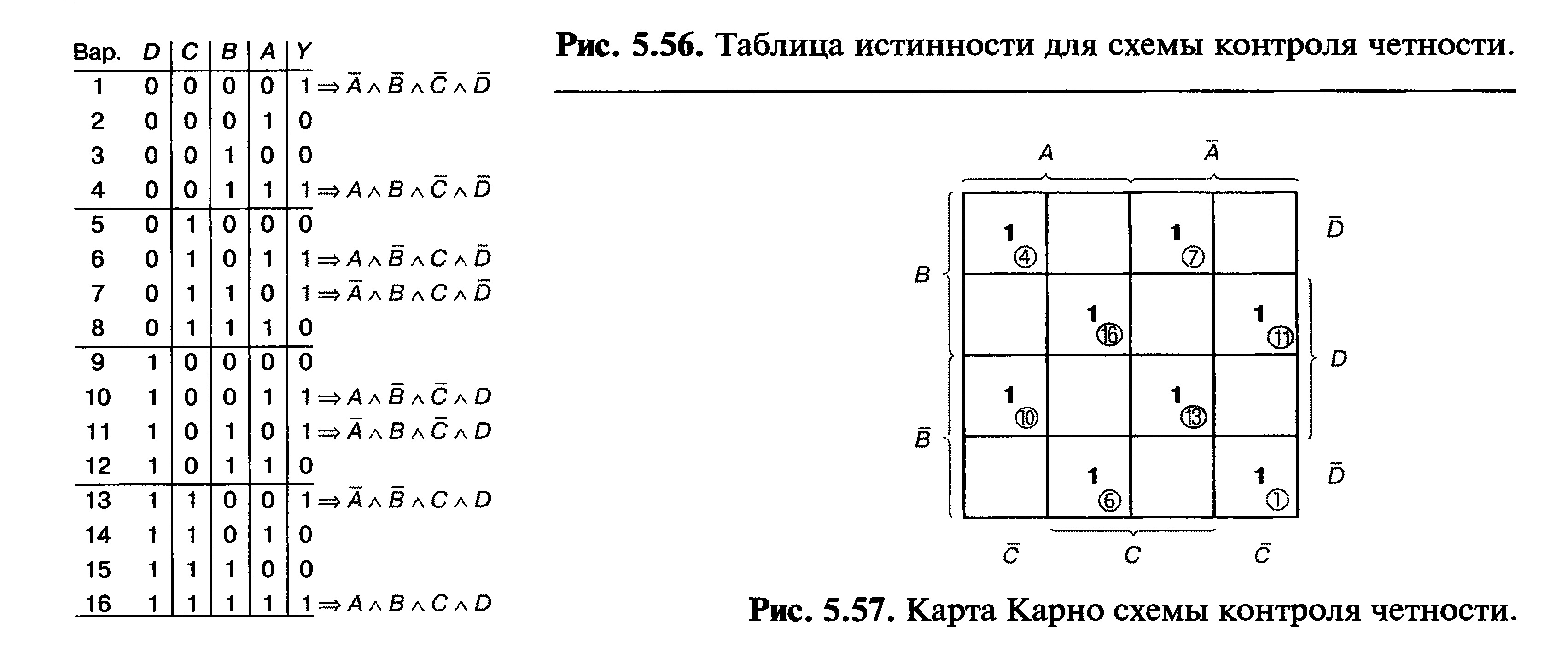

Требуется синтезировать схему с четырьмя входами. Входные переменные — А, В, С и D. Выходная переменная — Y.

Сначала нужно составить таблицу истинности. Y всегда будет равен 1, если 0, 2 или 4 входные переменные равны 1 (рис. 5.56).

Из таблицы истинности получается нормальная форма ИЛИ:

Y = {А л В лС л D}\/ ^А л В лС л {А л В лС л {А л В аС л

v{A л В лС л [А л В лС л {А л В лС л (А л В лС л D).

Отдельные полные конъюнкции пронумерованы. Попробуем упростить нормальную форму ИЛИ с помощью карты Карно (рис. 5.57). Здесь мы столкнулись с редким случаем, когда образование групп невозможно. Значит, данная нормальная форма ИЛИ не упрощается, и ее схема приведена на рис. 5.58.

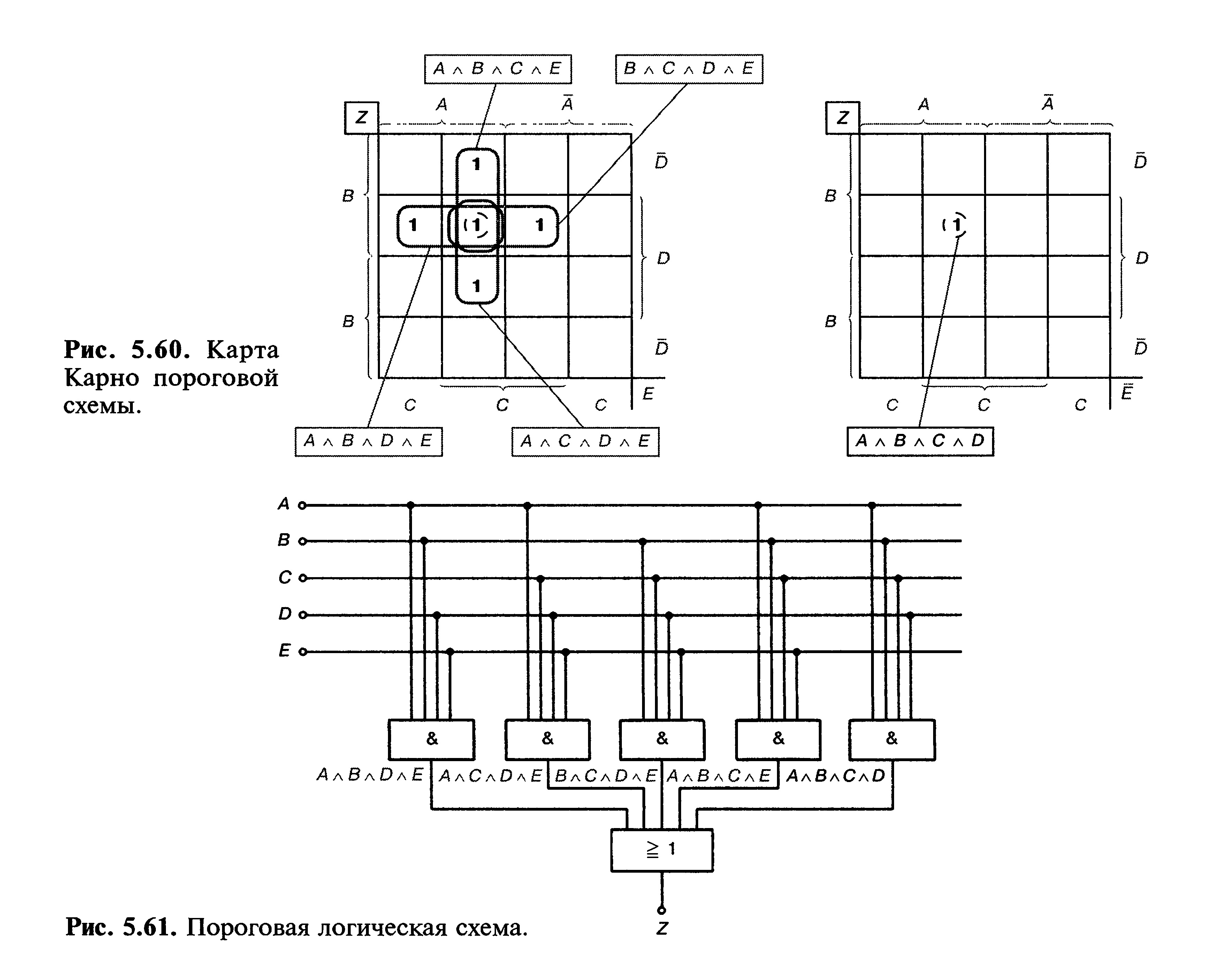

Пороговой логической схемой называется схема, в которой определенное

минимальное количество входных переменных должно иметь состояние 1,

чтобы на выходе появилась логическая 1.

Например, нужно рассчитать схему с пятью входными переменными. На

выходе должна быть 1 только тогда, когда по меньшей мере на 4 входах

присутствует 1.

Входные переменные имеют имена А, В, С, D и Е. Выходная переменная

— Z. Сначала нужно определить таблицу истинности. При пяти

переменных величинах возможны 32 варианта (рис. 5.59):

Z =¦ {А л В лС л D л E^v (А л В лС л D л E}v {А л В лС л D л v^A

л В лС л D л E^v [А л В лС л D л E^v (А л В лС л D л Е).

Нормальная форма ИЛИ состоит из шести полных конъюнкций.

Нормальная форма ИЛИ упрощается с помощью диаграммы Карно (рис. 5.60).

Можно образовать 5 двойных групп. Получается следующая упрощенная

логическая функция:

Z = (A aBaCaE)v (A aBaDaE)v (A aBaCaD)v v(A аС a D a E)v (В аС a D а Е).

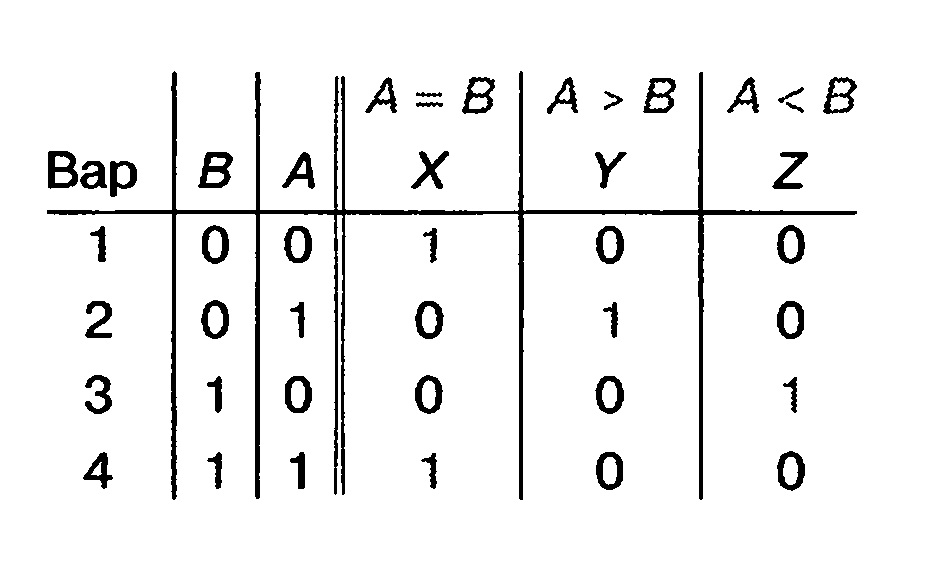

Схема для упрощенной функции представлена на рис. 5.61. Данное

уравнение можно еще упростить с помощью алгебры логики. Для первых трех

полных конъюнкций можно вынести за скобки (АаВ), для двух последних

— (С л D). Получается функция:

Z = [{А А В) А ((С А Е) V (D А Е) А С А Х>))] V [(С A D) А ((А А Е)

V (В А Я))]. Все-таки существенного упрощения добиться не удалось.

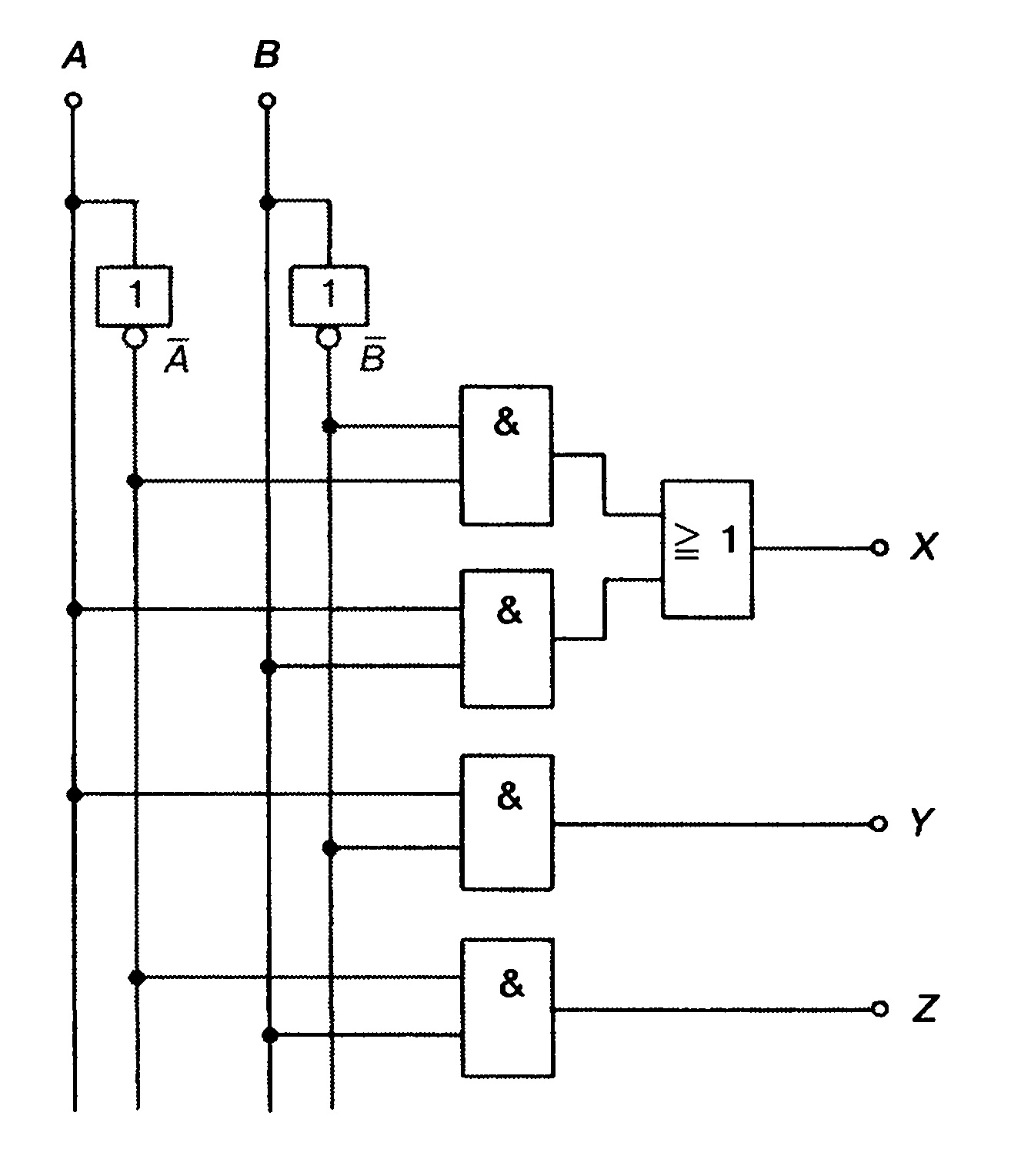

Схема сравнения (компаратор)

В цифровой технике часто нужно сравнить цифровые данные друг с

другом. Самая простая схема сравнения, так называемый компаратор,

сравнивает состояние двух переменных друг с другом.

Пусть переменные обозначены А и В. А и В могут быть равны. А может быть

больше, чем В и наоборот. Компаратор имеет для этих трех возможных

вариантов три выхода. Они обозначаются X, Y и Z и их состояния

присваиваются следующим образом:

А = Я=> Х = 1;

А > В^> Y= 1;

А < В => Z = 1.

Итак, необходимо синтезировать схему с двумя входными переменными А и В и с выходными переменными X, Y и Z.

При формировании таблицы истинности следует соблюдать правила: А

больше, чем В, если А = 1 и В = 0. Соответственно В больше, чем А, если

В = 1 и А = 0. Таблица истинности показана на рис. 5.62.

Из таблицы истинности получаются логические функции:

X = (AaB)v(AaB);

Y = А а В;

Z = А а В.

Эти уравнения далее не упрощаются Искомая схема показана на рис. 5.63.

Рис. 5.62. Таблтца истинности компаратора

Рис. 5.63. Схема компаратора

Схема сортировки транзисторов

Перед отправкой с завода транзисторы проверяются на соответствие

четырех важных параметров А, В, С и D диапазону допустимых значений.

Для измерения применяют четыре цифровых датчика. Датчик выдает 1, если

измеряемая величина находится в пределах диапазона допустимых значений.

Если измеряемая величина находится вне диапазона допустимых значений,

то датчик выдает 0.

Сортировка транзисторов происходит с помощью цифровой схемы. Если все

четыре величины находятся в пределах диапазона допустимых значений, на

выходе переменная М получает состояние 1. Если только В находится вне

диапазона допустимых значений, то выходная переменная N получает

состояние 1. Если только В ж D находятся вне диапазона допустимых

значений, то выходная переменная U получает состояние 1. Во всех других

случаях выход Z— 1, что означает, что транзистор является

бракованным.

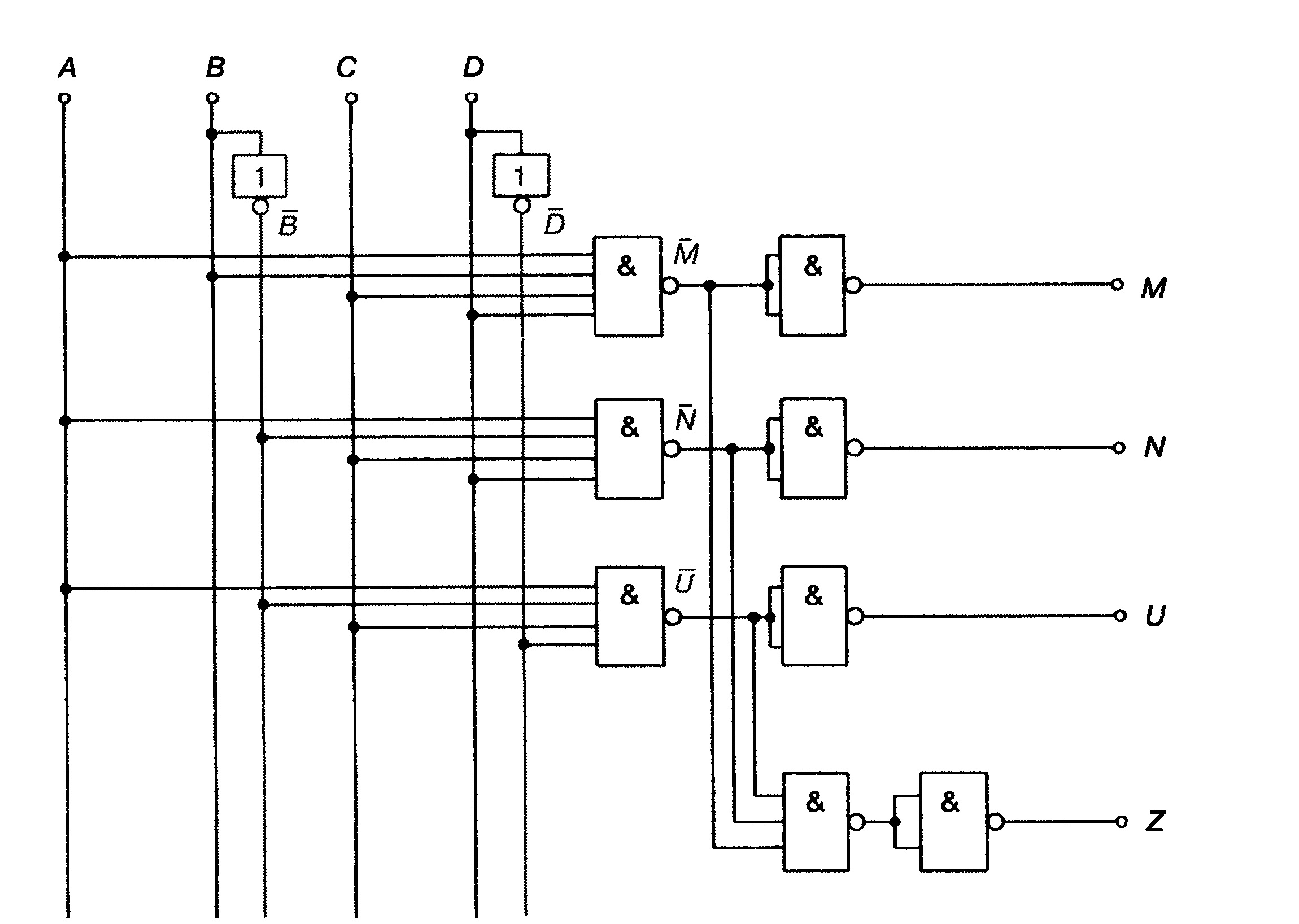

Требуется рассчитать схему и построить ее только на элементах И-НЕ (также говорят «в базисе И-НЕ»).

На вход поступают четыре переменные А, В, С и D. Выходными переменными

являются М, N, U и Z. М становится равной 1, если А= 1, 5 = 1, С = 1 и

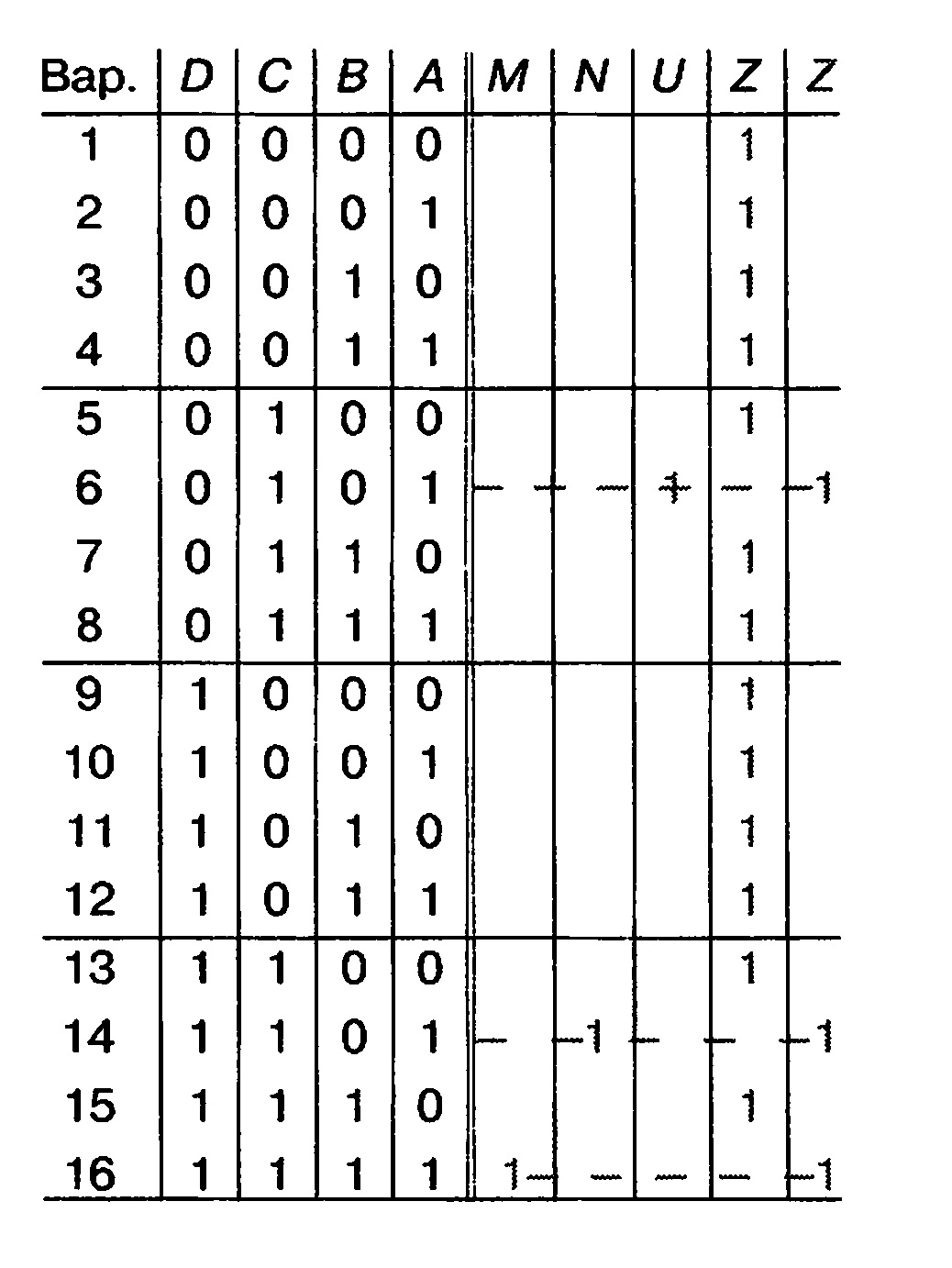

D = 1. Это вариант 16 в таблице истинности (рис.

5.64). будет 1, если А= \, 5=0, С = 1 и D = 1 (вариант 14). U будет равна 1, если А — 1, 5 = 0,

С = 1 и D = 0 (вариант 6). Во всех остальных случаях, кроме 6, 14 и 16, Z— 1.

Рис. 5.64. Таблица истинности для схемы сортировки транзисторов. Для большей наглядности нули для выходной переменной не записаны

В результате получаются следующие логические функции:

M = AaBaCaD;

N = А а В а С a D; U = А а В аС a D. Функция Z содержит 13 полных

конъюнкций. Z всегда тогда 1, если ни М, ни N, ни U не равняются 1.

Лучше записать нормальную форму ИЛИ для Z (см. рис. 5.64):

Z = (^4a5aCaD)v^a5aCaD^v^aBaCaZ));

Z = М v N vU. Тогда для прямого значения Z:

Z = М v N vU.

Рис. 5.65. Схема сортировки транзисторов

Найденные функции для М, Nn U упростить нельзя. Они должны быть пересчитаны вместе с уравнением для Z на базис И-НЕ:

М = AaBaCaD\

N = А а В аС л D;

U = АлВлСлО',

Z = М v N v U = М а N aU;

Z = М а N a U.

Из этих уравнений получается схема, представленная на рис. 5.65.

Посредством выходов М, N, U и Z может управляться механическое

устройство, которое распределяет транзисторы в 4 различные контейнера.

Похожие статьи