Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Свойства схем

Схемы каждого семейства имеют общие типичные свойства. На основе

этих свойств для решения определенных задач выбираются схемы

определенного семейства.

Важными свойствами, например, являются быстродействие и

помехоустойчивость. Для схемы управления лифтом неважно, срабатывает

схема в течение 0,1 мкс или 0,5 мкс. Важно, чтобы не происходило

ложного срабатывания. Поэтому целесообразно выбрать в данном случае

медленную, но более помехоустойчивую схему. Для компьютера желательны

схемы одновременно и быстродействующие, и помехоустойчивые. Два этих

качества являются взаимоисключающими, поэтому ищется компромисс между

скоростью и помехоустойчивостью.

Потребляемая мощность

Большие цифровые схемы потребляют много энергии. Если отдельный

логический элемент потребляет всего 10 мВт, то схема из 100000

элементов — уже 1 кВт. Компьютерам же с их 106 элементами в таком

случае требуется 10 кВт — об аккумуляторных батареях придется

забыть.

Если ограничить мощность питания отдельных логических элементов, то это

скажется на скорости работы схемы и ее помехоустойчивости. Время

переключения будет больше, и вследствие вынужденного использования

более низких уровней напряжения снизится помехоустойчивость.

Элементы различных семейств сильно различаются по своему

энергопотреблению. При обсуждении семейств в разделах 6.5—6.8 мы

еще вернемся к этому вопросу.

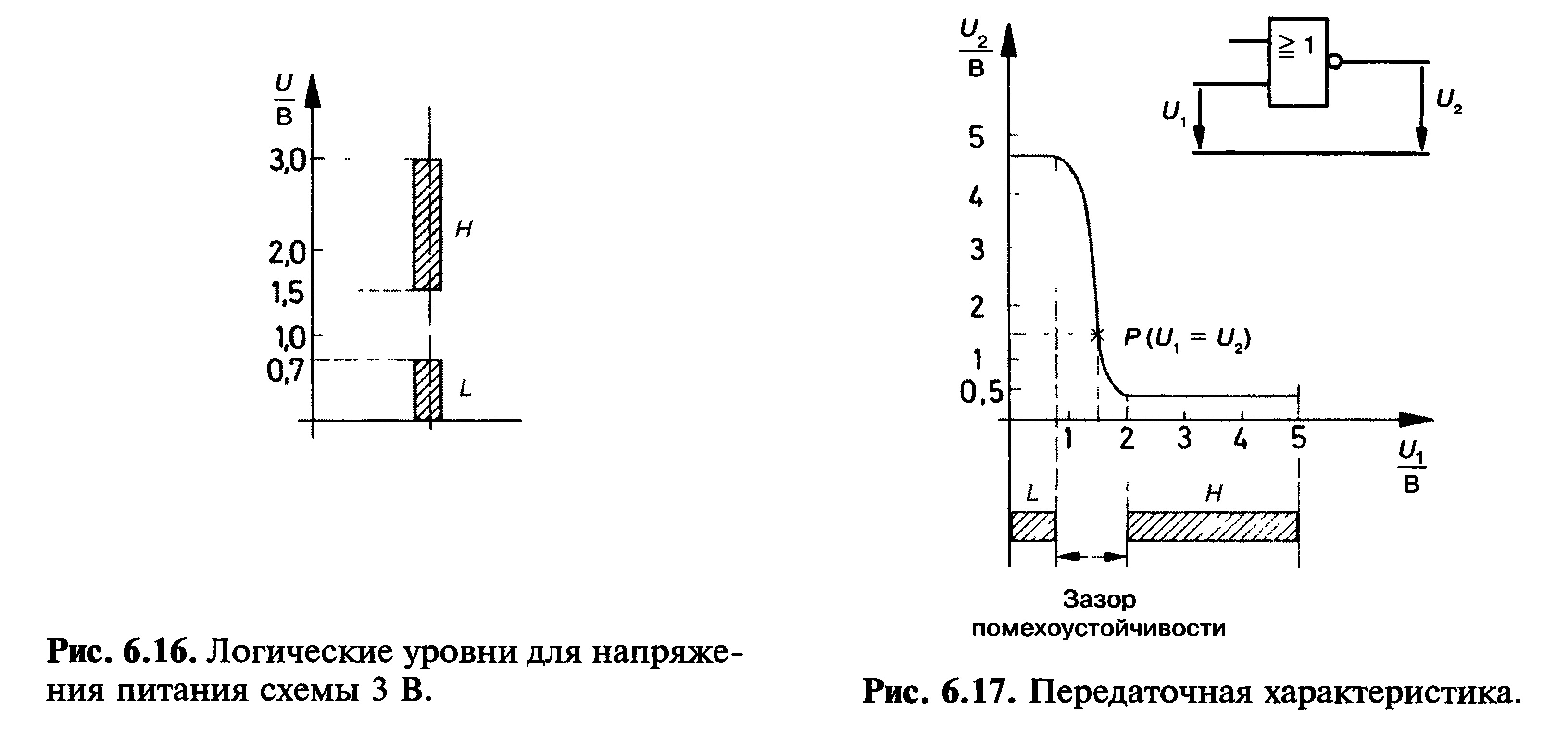

Диапазон уровней и передаточная характеристика

Для малого энергопотребления должно быть низкое напряжение питания. Напряжение питания определяет ВЫСОКИЙ уровень Н. НИЗКИЙ уровень L определяется падением напряжения на открытых диодах и транзисторах.

Если выбрать напряжение питания схемы 3 В, то ВЫСОКИЙ уровень Н

равен примерно 3 В. При подключении нагрузки на выход схемы и

протекании тока по элементам ВЫСОКИЙ уровень Н падает. Можно

максимально допустить падение до 1,5 В, при дальнейшем падении

напряжения зазор между ВЫСОКИМ и НИЗКИМ уровнями станет недопустимо мал

(рис. 6.16). Область НИЗКОГО уровня L определяется падением напряжения

на открытых диодах и транзисторах и находится в пределах от 0 В до +0,7

В.

Для основных семейств типовым является напряжение питания 5 В и выше.

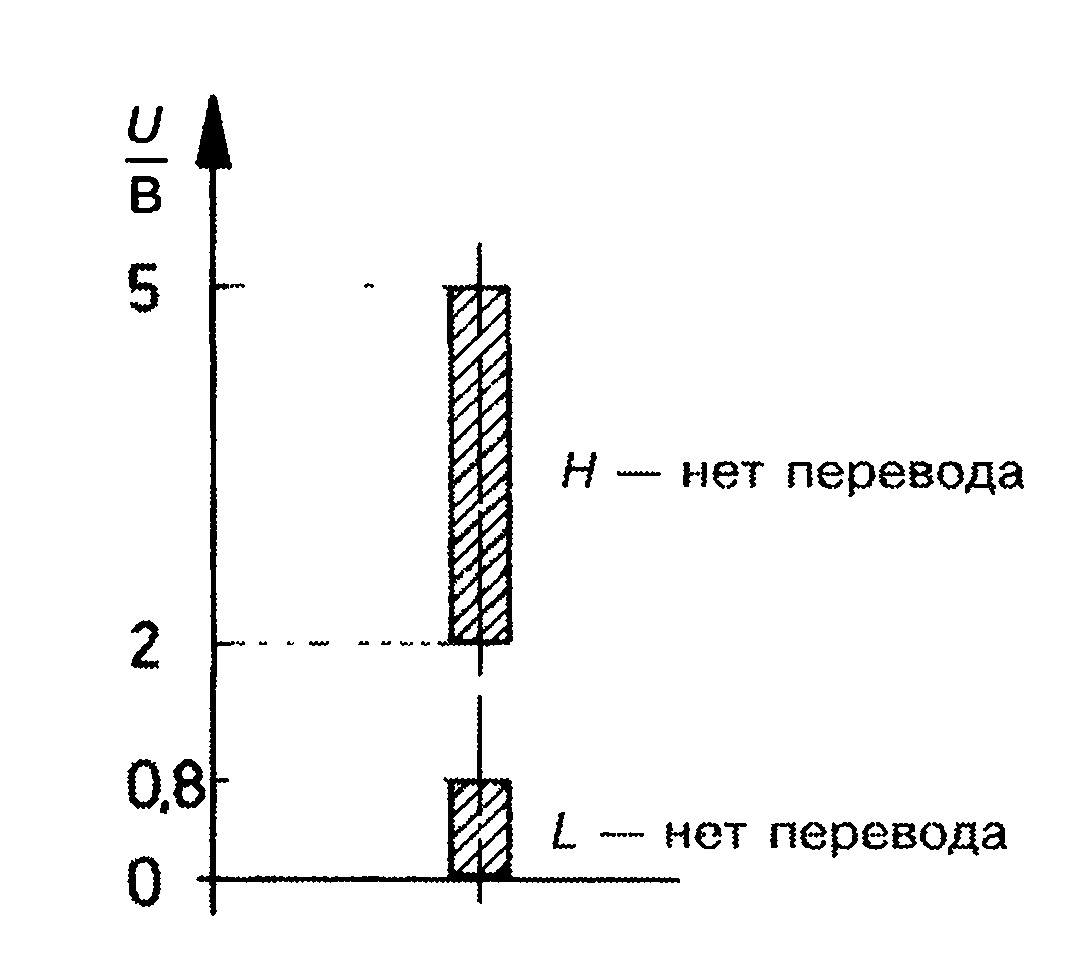

Для схем указывается так называемая передаточная характеристика,

изображенная на рис. 6.17. На вертикальной оси отложено выходное

напряжение U2, на горизонтальной оси — входное напряжение Uv

По передаточной характеристике можно определить Н- и L-уровни.

НИЗКИЙ уровень L согласно характеристике рис. 6.17 мог бы занимать

диапазон от 0 В до 1,5 В (точка Р), а ВЫСОКИЙ уровень Н- от 1,5 В до 5

В, если бы не необходимость в зазоре помехоустойчивости. Для лучшей

помехоустойчивости этот зазор должен быть как можно большим. Без зазора

помехи в виде импульсов напряжения могли бы вызывать самопроизвольные

переключения уровней с Н на L и наоборот. Кроме того, передаточная

характеристика зависит от температуры и тока нагрузки. Точка Р может

перемещаться. Обычно в качестве ширины зазора помехоустойчивости

выбирается длина участка падения С/, характеристики. Таким образом,

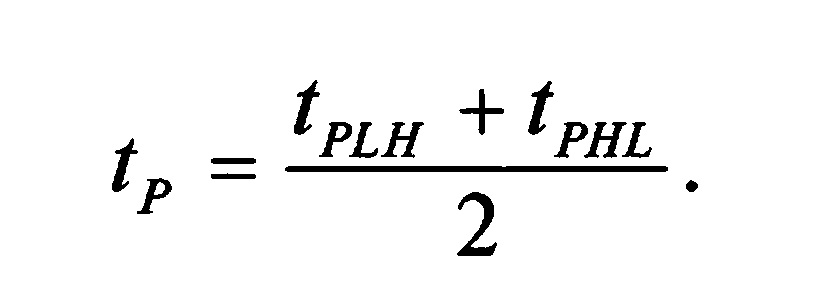

допустимый диапазон НИЗКОГО уровня L равен от 0 В до 0,8 В, а ВЫСОКОГО

Н — от 2 В до 5 В (рис. 6.18). Производители обычно немного

уменьшают допустимые диапазоны уровней напряжений с целью повышения

помехоустойчивости.

Рис. 6.18. Диапазоны уровней и передаточной характеристики

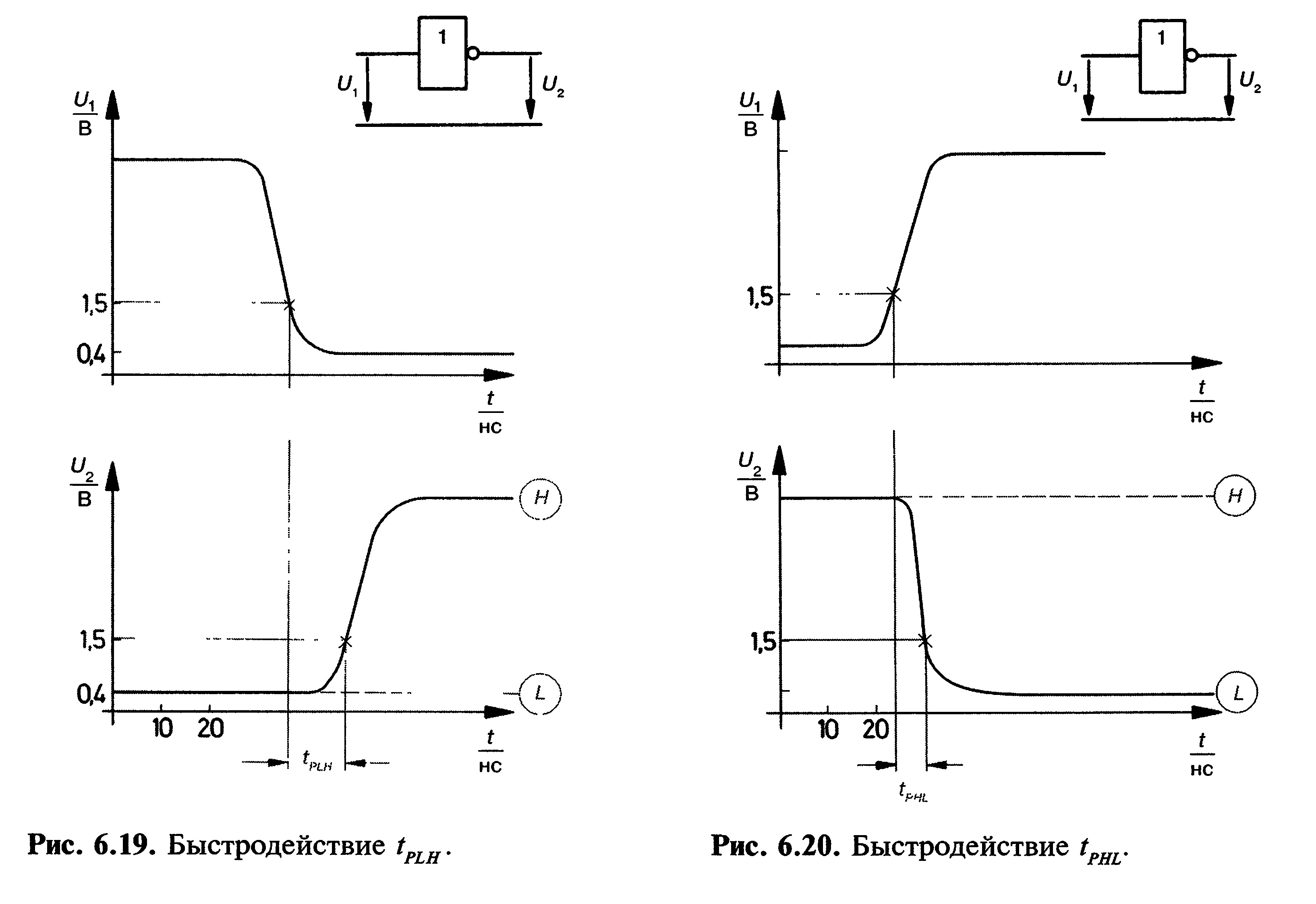

Время переключения

Скорость работы схемы определяется временем переключения ее

логических элементов. Различают понятия быстродействия логического

элемента, т. е. время реакции элемента на изменение сигнала на входах

tp, и время нарастания сигнала — tT

Быстродействие tPLH характеризует время задержки выходного сигнала по

отношению к входному при изменении состояния выхода с L на Н.

Соответственно tPHL характеризует время задержки выходного сигнала по

отношению к входному при изменении состояния выхода с Н на L.

Для измерения быстродействия используют относительный уровень 1,5 В.

Рис. 6.19 показывает, что быстродействие tPLH характеризует время, за

которое на выходе появляется напряжение входа 1,5 В. Характеристика для

tpHL представлена на рис. 6.20. Среднее быстродействие tp определяется

следующим образом:

Вместо термина «быстродействие» также применяется термин «время задержки сигнала».

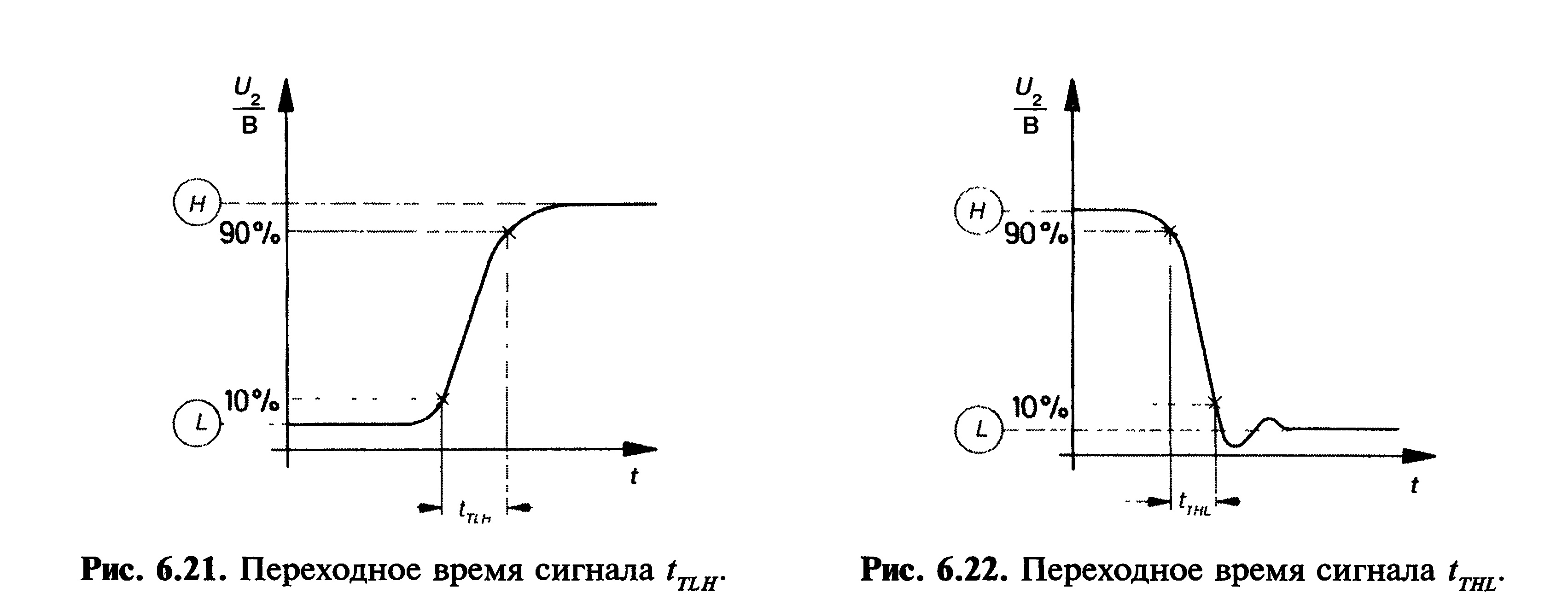

Переходное время сигнала относится только к выходу элемента. Оно характеризует крутизну фронтов выходного напряжения.

Время нарастания сигнала tTUj характеризует время, необходимое для возрастания выходного напряжения с 10 % до 90 % разницы между L и Н.

Время tTLH показано на рис. 6.21. Время нарастания сигнала tTHL характеризует время, необходимое для уменьшения выходного напряжения с 90 до 10 % разницы между L и Н (рис. 6.22).

Нагрузочная способность

Для управления логическими элементами требуются определенные

напряжения и токи. К выходу элемента может присоединяться только

определенное количество входов. Если подключить больше входов, то

выходной уровень недопустимо снизится. Элементы будут перегружены, а

схема работать не будет.

Различают два нагрузочных коэффициента: входной нагрузочный коэффициент

и коэффициент разветвления по выходу. Для каждого семейства схем

определена номинальная входная токовая нагрузка элементов. Для

TTJI-элементов:

Уровень L на входе 0,4 В — 1,6 мА Уровень Н на входе 2,4 В — 40 мкА.

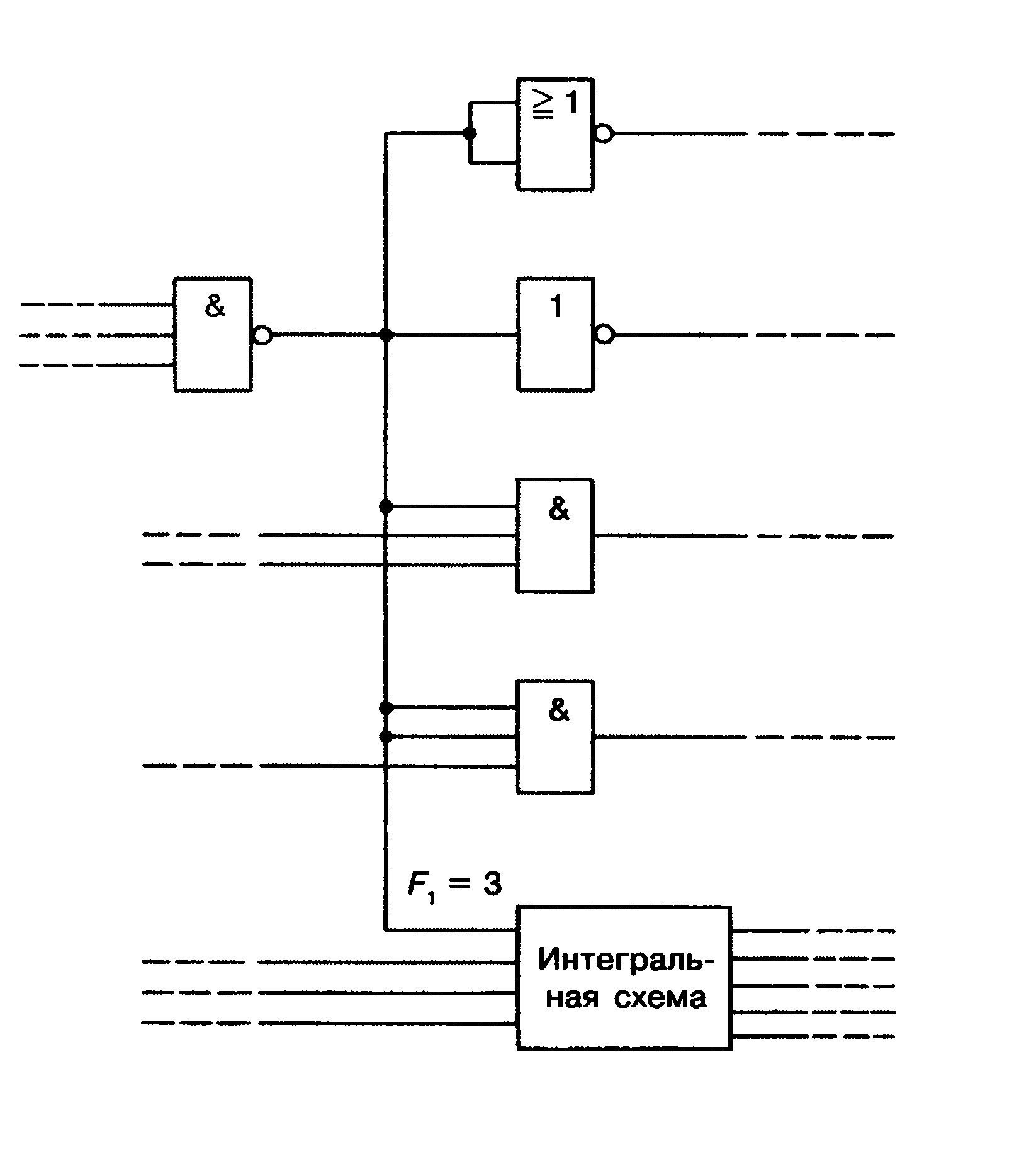

Входной нагрузочный коэффициент логического элемента равен единице (F]

= 1), если вход элемента потребляет номинальную мощность.

Специальные входы могут потреблять двойную или тройную номинальную

мощность. Тогда их нагрузочный коэффициент равен двум и соответственно

трем. Такие нагрузочные коэффициенты встречаются прежде всего в

интегральных схемах с высокой плотностью элементов.

Под коэффициентом разветвления логического элемента по выходу Fa

понимают количество нормальных входов других элементов, которое может

быть подключено к его выходу.

Нормальным для стандартных логических элементов считается коэффициент

разветвления не менее 10. Силовые логические элементы имеют коэффициент

разветвления не менее 30.

Пример ------------------------------------------------------------------

Элемент И-НЕ на рис. 6.23 имеет коэффициент разветвления, равный 10.

Сколько элементов дополнительно можно подключить к его выходу?

Рис. 6.23. Определение коэффициента разветвления логического элемента

Верхний элемент ИЛИ-HE имеет два объединенных входа. Каждый вход

имеет единичный нагрузочный коэффициент. Значит, этот элемент нагружает

выход серого элемента двойной номинальной нагрузкой. Аналогичные

рассуждения можно применить к нижнему элементу И. Суммарно к выходу

элемента И-НЕ подключено шесть одинарных входов и один вход с Ft= 3. То

есть девять номинальных входных нагрузок.

Можно присоединить еще один вход с Fj = 1.

Помехоустойчивость

Помехи в виде импульсов напряжения могут вызывать самопроизвольные

ложные переключения выходов логических элементов с Н на L и наоборот с

L на Н. Чтобы это не происходило, необходим зазор между допустимыми

диапазонами ВЫСОКОГО и НИЗКОГО уровней. Чем больше зазор, тем выше

помехоустойчивость схемы.

Различают статическую и динамическую (импульсную) помехоустойчивость.

Статическая помехоустойчивость элемента относится к импульсам

напряжения, действующим дольше средней длительности переходных

процессов в схеме tp К статическим помехам также относятся медленно

возрастающие импульсы напряжения.

Статическая помехоустойчивость характеризует максимально допустимое

изменение напряжения на входах элемента, при котором не происходит

изменение состояния выхода.

Она указывается для номинального режима работы и для самой

неблагоприятной комбинации влияющих на помехоустойчивость факторов.

Например, при неудачном соотношении напряжений управляющих и

управляемых логических элементов, неблагоприятном сочетании входных

сигналов, при неноминальной температуре окружающей среды и при

задействованном максимальном коэффициенте разветвления. Такую

комбинацию называют случаем худшей помехоустойчивости.

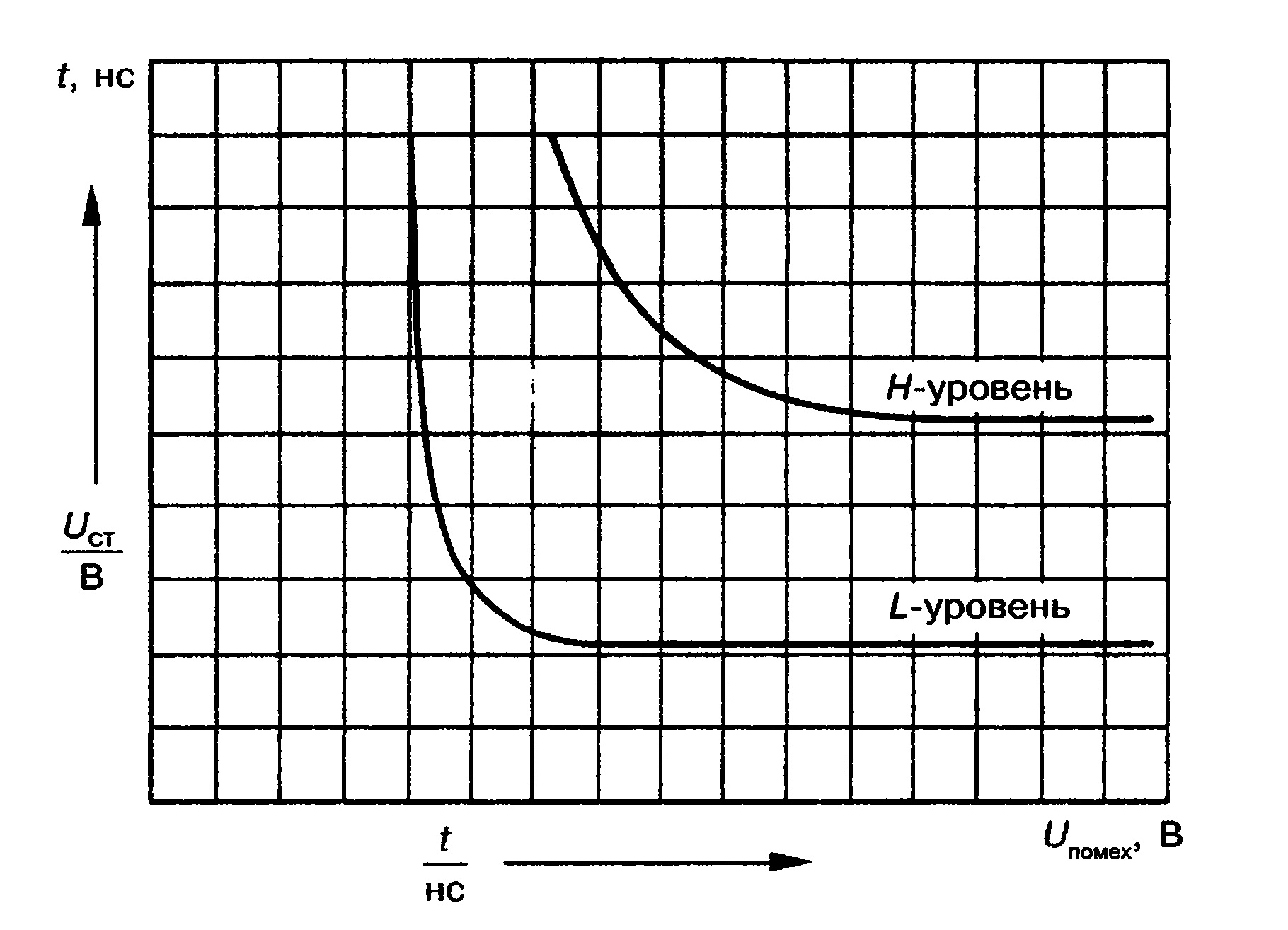

Динамическая помехоустойчивость элемента относится к импульсам

напряжения, длящимся меньше средней длительности переходных процессов в

схеме tp.

Рис. 6.24. Кривые динамической помехоустойчивости

Соответствующая импульсам энергия, характеризуемая амплитудой и

длительностью импульса, не должна превышать определенное предельное

значение. Динамическая помехоустойчивость зависит в основном от

чувствительности входа логического элемента. Она описывается граничной

кривой (рис. 6.24).

Динамическая помехоустойчивость характеризует длительность помехи по

напряжению определенной величины на входах элемента, при которой не

происходит изменение состояния выхода.

Точные данные для допустимой амплитуды напряжения помехи и допустимое

время ее действия получают из анализа характеристик (рис. 6.24).

При этом существуют кривые для Я-уровня и Z-уровня. Если на входе

действует состояние Н, то следует пользоваться кривой для //-уровня.

Соответственно если на входе действует состояние L, то следует

пользоваться кривой для ^-уровня, //-уровни более помехоустойчивы,

поэтому кривая для Н-уровня проходит выше.

Проводные логические операции

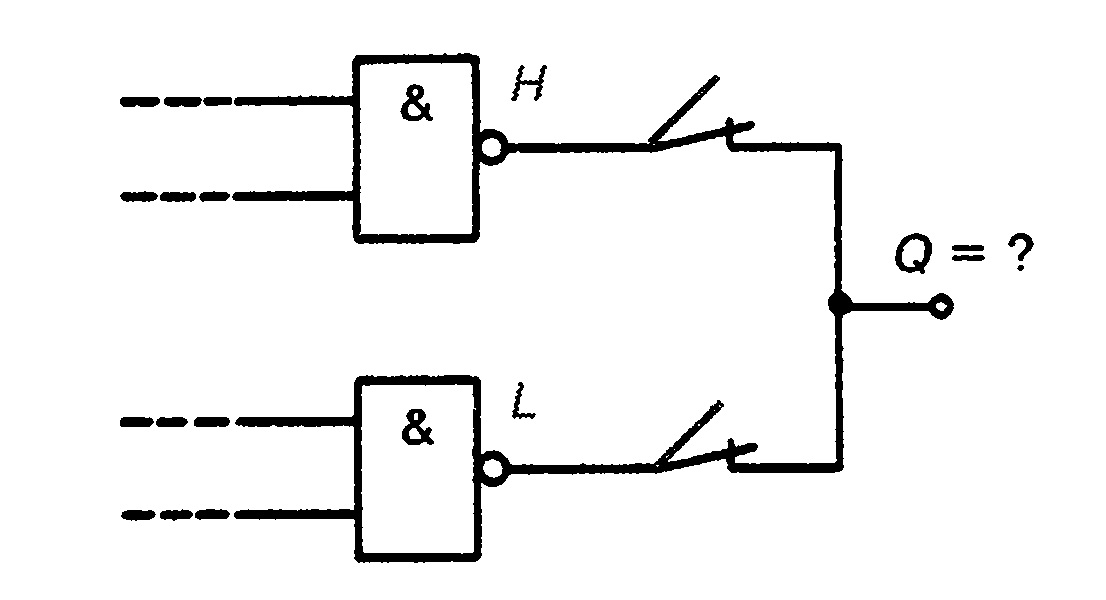

Если выходы двух элементов связаны гальванически, т. е. просто

соединены проводником, то образуется логическая связь, которая в

зависимости от внутреннего строения схемы представляет из себя операции

И или ИЛИ.

Если выход одного элемента имеет состояние Н, а другой выход —

состояние L (рис. 6.25), то состояние точки Q не определено. Какое

состояние примет эта точка — зависит от технических данных схемы.

Допустим, что уровень L соответствует заземлению, 0 В, а уровень Н-напряжению питания (например +5 В).

Если выход, на котором действует состояние L, имеет малое сопротивление

относительно земли, т. е. 0 В, то //-состояние другого выхода будет

заземлено и точка Q примет состояние L. Говорят, при этих элементах

доминирует уровень L.

В этом случае Q может иметь состояние //только тогда, когда оба выхода

имеют состояние Н. Такое соединение называется проводное И (при

положительной логике).

Рис. 6.25. Гальваническая связь выходов двух элементов «И-НЕ»

Если в схеме доминирует уровень L, то при проводной связи на выходе

выполняется логическое умножение И — при условии положительной

логики.

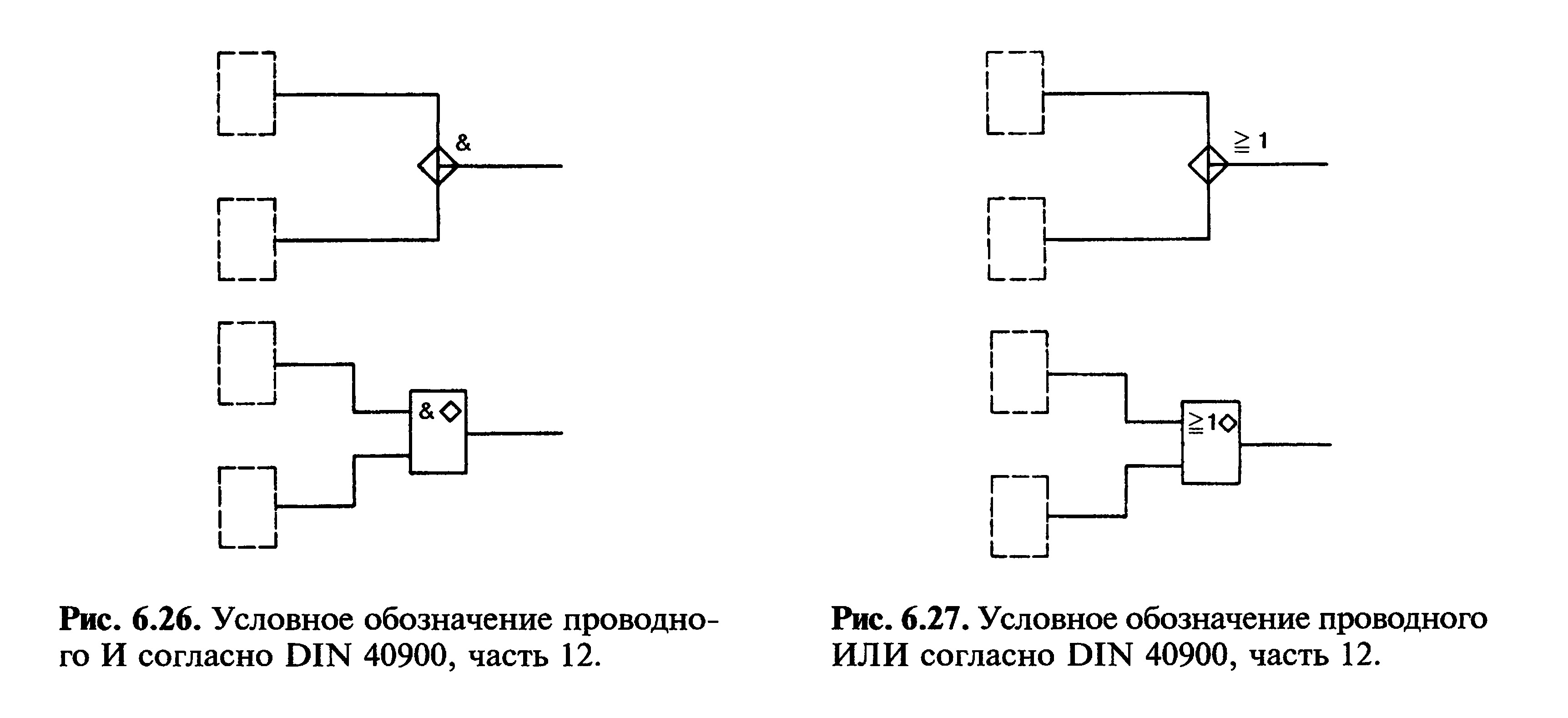

Проводное И изображено на схемах (рис. 6.26). Для его обозначения возможны два варианта на выбор.

Если выход, на котором действует состояние Н, имеет малое сопротивление

относительно источника питания, то L-состояние другого выхода будет

поднято до //-уровня и точка Q (см. рис. 6.25) примет состояние Н. В

этом случае говорят, что при этих элементах доминирует уровень //.

Такое соединение называется проводное ИЛИ (при положительной логике).

Если в схеме доминирует уровень Н, то при проводной связи на выходе

выполняется логическое сложение ИЛИ — при условии положительной

логики.

Два варианта обозначения проводного ИЛИ представлены на рис. 6.27.

Точка Q может принимать при определенной структуре схемы уровень,

находящийся между диапазонами //-уровня и L-уровня. В таких схемах

проводная связь выходов применяться не может. Проводное ИЛИ и проводное

И в таких схемах запрещены.

При снижении выходного уровня с Я на I на выходе с предыдущим

состоянием Н может течь недопустимо высокий ток. Также при повышении

выходного уровня с i на Я на выходе с предыдущим состоянием L может

течь недопустимо высокий ток. Логические элементы вследствие этого

будут перегружены по току.

Проводные соединения выходов, образующие проводные И и проводные ИЛИ,

могут производиться только при разрешении производителя.

В каких случаях разрешаются проводные логические соединения,

указывается в технических описаниях. Проводные логические операции

ведут к упрощению схемы, к уменьшению времени коммутации и к сокращению

производственных расходов.

Похожие статьи