Электростанции

Навигация

-

Меню сайта

- Организация эксплуатации

- Электрические схемы

- Турбогенераторы

- Трансформаторы и автотрансформаторы

- Распределительные устройства

- Электродвигатели

- Автоматика

- Тепловая изоляция

- Регулирование энергоблоков

- Тяговые подстанции

- Выпрямители и зарядные устройства

- Проектирование электрических сетей и систем

- Электрооборудование электротермических установок

- Электрооборудование земснарядов

- Цифровая электроника

Элементы задержки

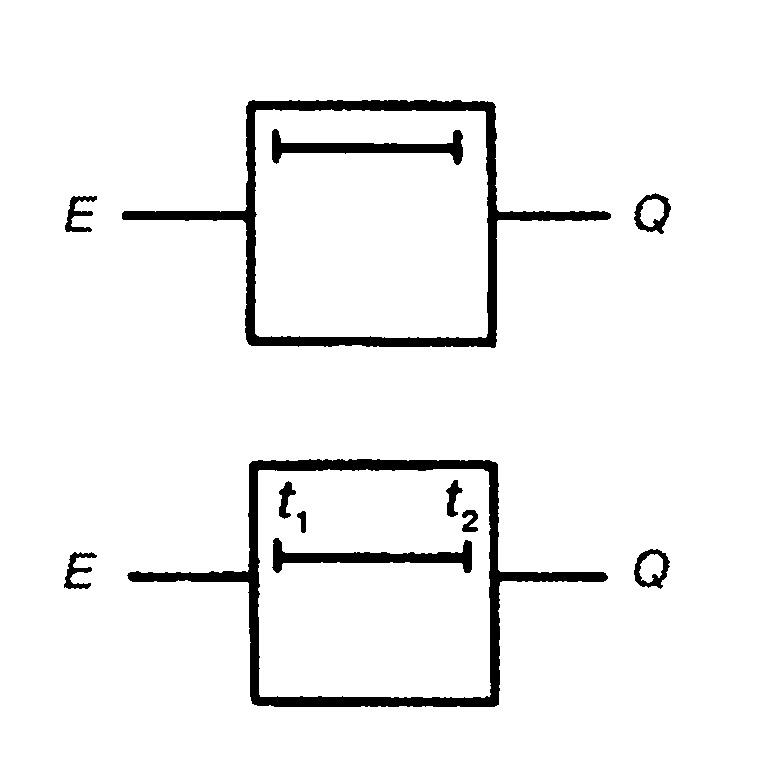

Логические элементы задержки, как следует из названия, задерживают прохождение сигнала. Если на входе элемента задержки происходит переход сигнала с 0 на 1, то через определенное время выход элемента меняет состояние с 0 на 1. Изменение сигнала с 1 на 0 на входе вызывает через время t2 изменение сигнала с 1 на 0 на выходе. Условное обозначение элемента задержки приведено на рис. 7.114. Верхнее условное обозначение применяется для всех элементов задержки вообще. Нижнее условное обозначение содержит времена tx и tr Вместо и t2 могут стоять фактические времена задержки.

Рис. 7.114. Условное обозначение элемента задержки

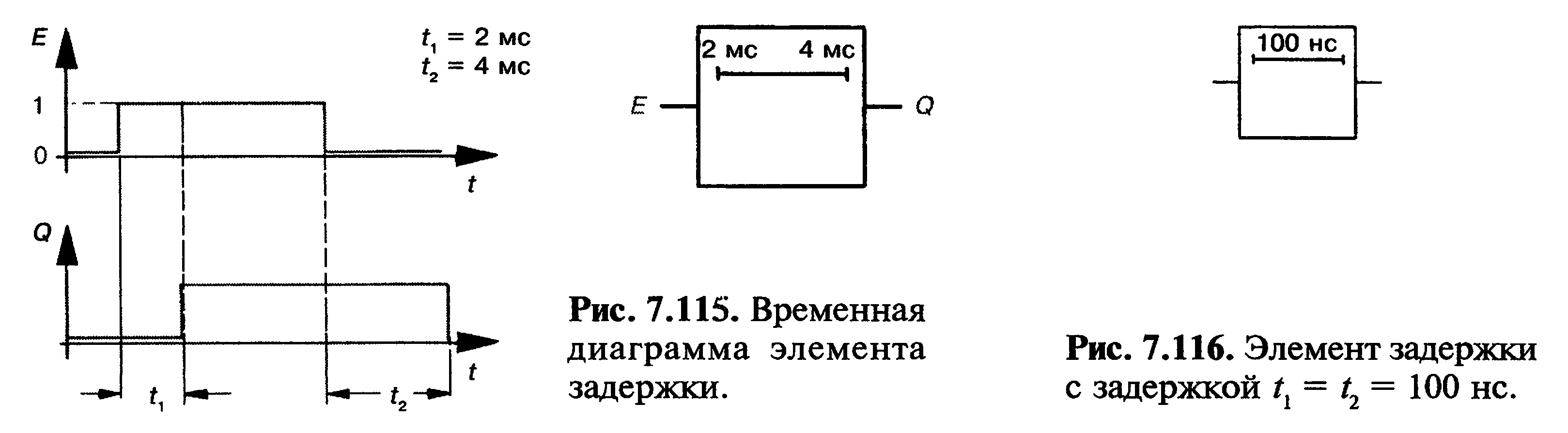

Элемент задержки на рис. 7.115 имеет время задержки /, = 2 мс и время задержки t2 = 4 мс. Соответствующие временные диаграммы показывают запаздывание сигналов. Если времена t{ и t2 одинаковы, то в условном обозначении можно поставить только одно время (рис. 7.116).

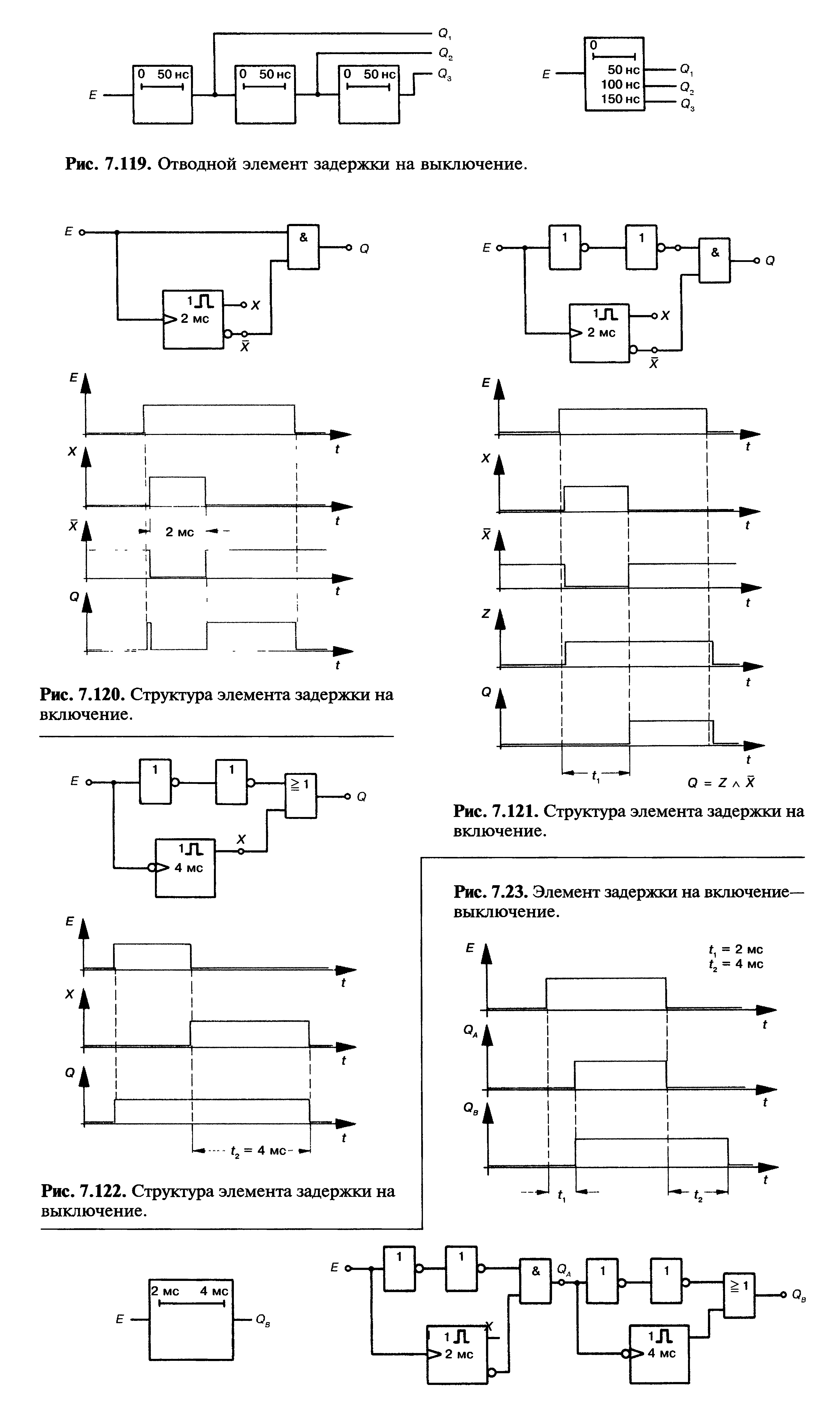

Часто необходимы так называемые элементы задержки на включение. Эти элементы задерживают на определенное время tt передний фронт сигнала. Обратный фронт проходит без запаздывания t2 — 0 (рис. 7.117).

Кроме элементов задержки на включение имеются также элементы задержки на выключение. Они задерживают на определенное время t2 обратный фронт сигнала. Передний фронт проходит без запаздывания tx = 0 (рис. 7.118).

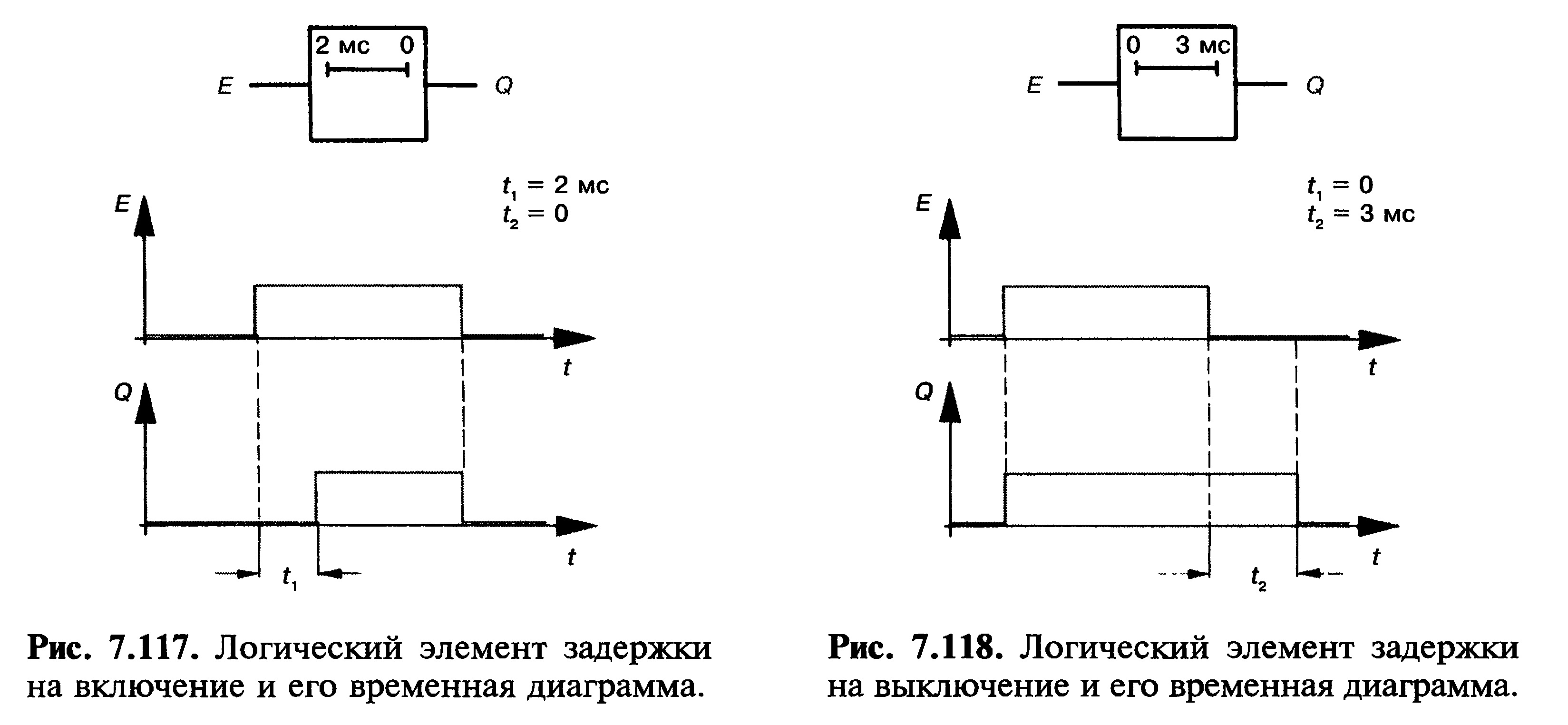

Также производятся элементы задержки с несколькими различными временами задержки. Такие элементы называются отводными элементами задержки. На рис. 7.119 показана структура и условное обозначение такого элемента задержки. Отводной элемент задержки построен на нескольких простых элементах задержки.

Похожие статьи